Difference between revisions of "Channel Shortening Prefilter"

From iis-projects

m (Weberbe moved page Channel Shortening ASIC to Channel Shortening Prefilter) |

|

(No difference)

| |

Revision as of 10:52, 24 March 2015

Contents

Short Description

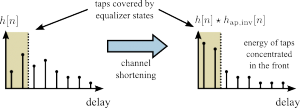

In a wireless system with a multi-tap Channel Impulse Response (CIR) the receiver is confronted with a computationally challenging issue: Inter Symbol Interference (ISI) and Viterbi equalization. In particular as modern cellular standards tend to use ever higher modulation orders (up to 32-QAM) for Evolved EDGE, the equalizer becomes ever more complex. There exist various approaches to mitigate the induced ISI by a multi-tap CIR. The approach presented in [1] uses a channel shortening prefilter before equalization. Thus, ISI is mitigated to a large extent and the Viterbi equalizer's complexity is reduced. Said channel shortening prefilter has been thoroughly analyzed at the institute and a fix-point model has been built in MATLAB. In this project, the students ought to understand the channel shortening prefilter from [1] and implement it on an ASIC. The goal is to have an ultra-low power channel shortening prefilter.

Status: Available

- Looking for 1-2 Semester students

- Contact: Benjamin Weber

Prerequisites

- VLSI I

- MATLAB

Character

- 20% Theory/Simulation

- 50% VHDL

- 30% ASIC Implementation

Professor

References

[1] Fredrik Rusek, Adnan Prlja. Optimal Channel Shortening for MIMO and ISI Channels. In Wireless Communications, IEEE Transactions on, vol. 11, no. 2, pages 810–818, 2012.