Difference between revisions of "ASIC Implementation of High-Throughput Next Generation Turbo Decoders"

From iis-projects

| (6 intermediate revisions by 2 users not shown) | |||

| Line 14: | Line 14: | ||

[http://asic.ethz.ch/cg/2012/Jetfire.html Jetfire: Turbo Decoder for LTE-Advanced] | [http://asic.ethz.ch/cg/2012/Jetfire.html Jetfire: Turbo Decoder for LTE-Advanced] | ||

| − | + | <!-- | |

===Status: Available === | ===Status: Available === | ||

: Looking for 1-2 Semester/Master students | : Looking for 1-2 Semester/Master students | ||

: Contact: [[:User:Belfanti |Sandro Belfanti]] | : Contact: [[:User:Belfanti |Sandro Belfanti]] | ||

| − | + | ---> | |

| + | ===Status: Completed === | ||

===Prerequisites=== | ===Prerequisites=== | ||

: VLSI I | : VLSI I | ||

| Line 45: | Line 46: | ||

<!-- : [http://www.iis.ee.ethz.ch/portrait/staff/schenk.en.html Andreas Schenk] ---> | <!-- : [http://www.iis.ee.ethz.ch/portrait/staff/schenk.en.html Andreas Schenk] ---> | ||

<!-- : [http://www.dz.ee.ethz.ch/en/general-information/about/staff/uid/364.html Hubert Kaeslin] ---> | <!-- : [http://www.dz.ee.ethz.ch/en/general-information/about/staff/uid/364.html Hubert Kaeslin] ---> | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

[[Category:Digital]] | [[Category:Digital]] | ||

| − | [[Category: | + | [[Category:ASIC]] |

| + | [[Category:Telecommunications]] | ||

| + | [[Category:Completed]] | ||

[[Category:Semester Thesis]] | [[Category:Semester Thesis]] | ||

| − | [[Category: | + | [[Category:Master Thesis]] |

| − | + | [[Category:Belfanti]] | |

<!-- | <!-- | ||

Latest revision as of 11:12, 14 April 2016

Contents

Short Description

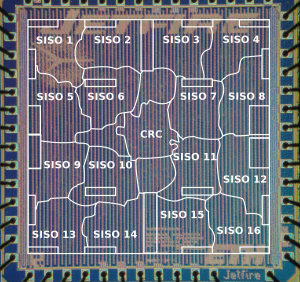

Forward error correction is a crucial part in any communication system, since it enables reliable transmission over unreliable channels. In mobile communications, most modern systems rely on turbo codes because of their outstanding error correction capabilities in conjunction with efficient decoder implementations. For the most recently developed standards with throughput requirements in excess of 1Gbps, providing the necessary throughput has become a real challenge. The IIS has a long history of high-throughput turbo decoders and we have recently had several new ideas on how to improve our architectures even further. In this project you will implement a proof-of-concept chip in VHDL, to demonstrate the efficiency of the new architectures. To that end, you can rely on the expertise from a long line of previous turbo decoders to hopefully develop an outstanding ASIC.

If you are interested in doing a thesis (semester or master) in the field of error correcting codes, such as turbo codes, just contact Sandro Belfanti or Christoph Roth. There are different projects available, ranging from more theoretical/simulation based projects to the VLSI implementation in form of chip design projects.

Previous Turbo Decoders

All the chips which have been fabricated can be found in the IIS chip gallery. Some examples for turbo decoders designed at the IIS are

LaLe: Turbo Decoder for TD-HSPA

LTE-Turbo: Turbo Decoder for LTE

Jetfire: Turbo Decoder for LTE-Advanced

Status: Completed

Prerequisites

- VLSI I

- MATLAB and VHDL is an advantage

Character

- 20% Simulation/Theory

- 50% VHDL

- 30% ASIC Implemenatation