Difference between revisions of "DigitalUltrasoundHead"

From iis-projects

(Created page with "==Short Description== In today's conventional 2D ultrasound imaging systems, the piezoelectric elements in the transducer head are connected to a backend system over a large c...") |

|||

| Line 10: | Line 10: | ||

In order to do so, the entire analog frontend of the ultrasound system needs to be integrated into the transducer head and a digital link needs to be designed. | In order to do so, the entire analog frontend of the ultrasound system needs to be integrated into the transducer head and a digital link needs to be designed. | ||

| − | Having all ultrasound specific hardware integrated in the transducer head, will allow to connect it over a standard interface | + | Having all ultrasound specific hardware integrated in the transducer head, will allow to connect it over a standard interface to a commodity platform for post processing. This new paradigm will enable new kinds of portable ultrasound systems. |

| + | |||

| + | ===Update - August 2016=== | ||

| + | Currently, we have assembled a first prototype: | ||

| + | |||

| + | [[File:LPi.jpg|center|400px]] | ||

| + | |||

===Status: Available === | ===Status: Available === | ||

| Line 20: | Line 26: | ||

==Detailed Task Description== | ==Detailed Task Description== | ||

| − | This is an ongoing project at our lab and we are looking for motivated students to contribute in the development: | + | This is an ongoing project at our lab and we are looking for motivated students to contribute in the development for the following tasks: |

| − | * | + | * FPGA design: for the FPGA (Artix 7) on the board shown above, and the FPGA in the backend system (Kintex Ultrascale 7) |

| − | + | * System level design: Microcontroller firmware programming (C) for the frontend using a soft-microcontroller core on the FPGA. Optical link between two FPGA boards. | |

| − | * | + | * PCB Design: power supply, next version of the board. |

If you are interested, contact us and we will setup a specific student project considering the current state of the project and the students interests. | If you are interested, contact us and we will setup a specific student project considering the current state of the project and the students interests. | ||

| − | == | + | Use this [http://iis-projects.ee.ethz.ch/index.php?title=Special%3ASearch&search=LightProbe link] to search for other projects associated to this project. |

| − | + | ||

==Links== | ==Links== | ||

Revision as of 13:12, 15 August 2016

Contents

Short Description

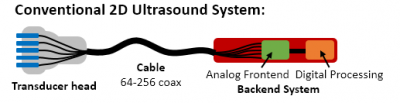

In today's conventional 2D ultrasound imaging systems, the piezoelectric elements in the transducer head are connected to a backend system over a large cable containing hundreds of small coaxial cables. This is shown in the figure below:

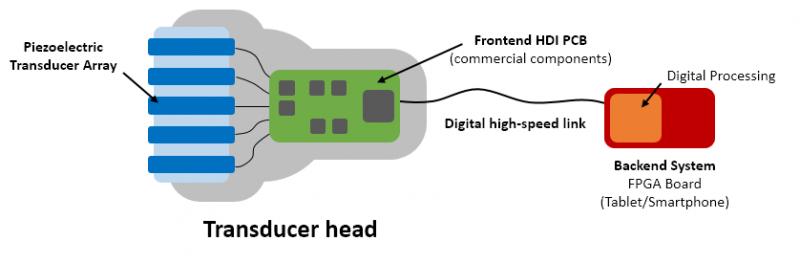

We plan to replace this analog connection by a digital link as shown in the next figure:

In order to do so, the entire analog frontend of the ultrasound system needs to be integrated into the transducer head and a digital link needs to be designed.

Having all ultrasound specific hardware integrated in the transducer head, will allow to connect it over a standard interface to a commodity platform for post processing. This new paradigm will enable new kinds of portable ultrasound systems.

Update - August 2016

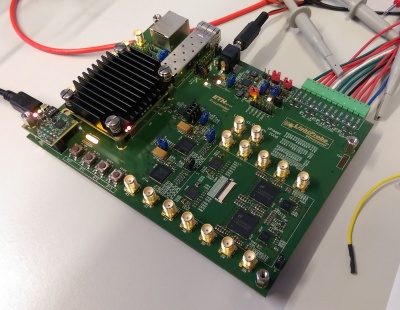

Currently, we have assembled a first prototype:

Status: Available

- Group Project/Semester/Master Thesis

- Supervision: Pascal Alexander Hager (IIS)

Professor

Detailed Task Description

This is an ongoing project at our lab and we are looking for motivated students to contribute in the development for the following tasks:

- FPGA design: for the FPGA (Artix 7) on the board shown above, and the FPGA in the backend system (Kintex Ultrascale 7)

- System level design: Microcontroller firmware programming (C) for the frontend using a soft-microcontroller core on the FPGA. Optical link between two FPGA boards.

- PCB Design: power supply, next version of the board.

If you are interested, contact us and we will setup a specific student project considering the current state of the project and the students interests.

Use this link to search for other projects associated to this project.