Difference between revisions of "Energy Efficient SoCs"

From iis-projects

(→Available Projects) |

|||

| Line 23: | Line 23: | ||

* '''e-mail''':[mailto:balasr@iis.ee.ethz.ch balasr@iis.ee.ethz.ch] | * '''e-mail''':[mailto:balasr@iis.ee.ethz.ch balasr@iis.ee.ethz.ch] | ||

* '''office''': ETZ J78 | * '''office''': ETZ J78 | ||

| + | |||

| + | ===[[:User:Pschiavo |Davide Schiavone]]=== | ||

| + | * '''e-mail''':[mailto:davide.schiavone@epfl.ch davide.schiavone@epfl.ch] | ||

| + | * '''office''': ESL 136, EPFL, Lausanne | ||

==Projects Overview== | ==Projects Overview== | ||

Revision as of 17:08, 15 August 2022

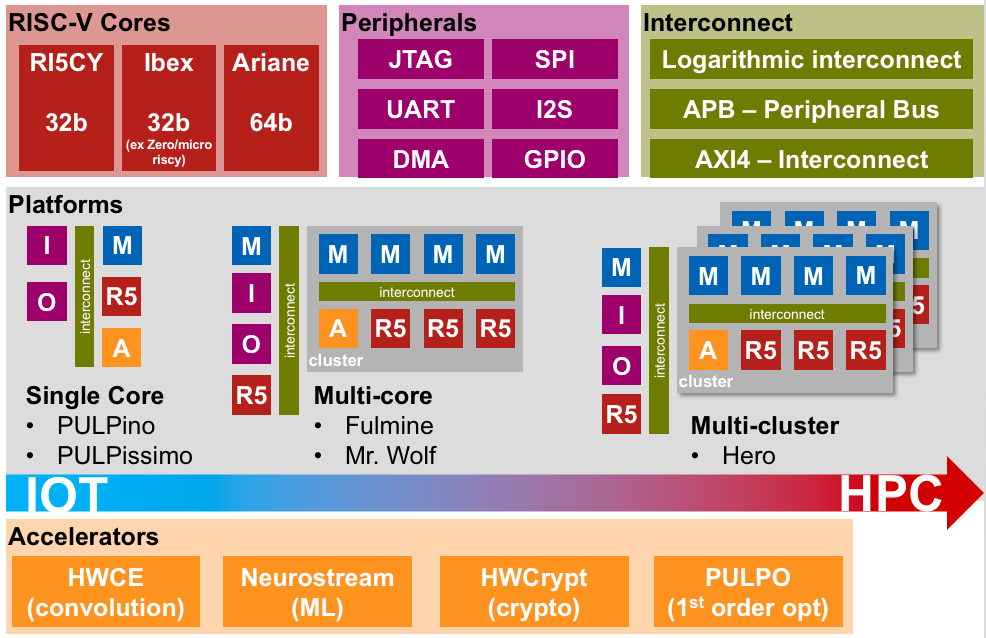

Energy Efficient Systems on Chip are one of the group's flagship research topics. With an increasing demand for near-sensor processing, the energy-boundedness of embedded IoT devices becomes an issue. The goal of this particular research field is to come up with new architecture for high-performance heterogeneous compute platforms that push the limits of energy-efficiency for digital signal processing and embedded machine learning applications. Under the brand PULP (parallel ultra low power) we are actively developing several single and multi-core RISC-V SoC architectures that combine the versatility of parallel general-purpose computing with the energy efficiency of application-specific hardware accelerators.

As part of our research activities we regularly tape-out PULP based SoC in various sizes, from smaller student tape-outs incorporating novel hardware accelerators to larger multi-cluster SoCs. On [1] you will find more details about this particular research aspect of the digital circuits group.

Contents

Manuel Eggimann

- e-mail:meggiman@iis.ee.ethz.ch

- phone: +41 44 632 99 58

- office: ETZ J68

Alfio Di Mauro

- e-mail:adimauro@iis.ee.ethz.ch

- office: ETZ J78

Robert Balas

- e-mail:balasr@iis.ee.ethz.ch

- office: ETZ J78

Davide Schiavone

- e-mail:davide.schiavone@epfl.ch

- office: ESL 136, EPFL, Lausanne

Projects Overview

Available Projects

Projects In Progress