Difference between revisions of "Fault-Tolerant Floating-Point Units (M)"

From iis-projects

Lbertaccini (talk | contribs) |

|||

| (5 intermediate revisions by 2 users not shown) | |||

| Line 4: | Line 4: | ||

[[Category:Acceleration_and_Transprecision]] | [[Category:Acceleration_and_Transprecision]] | ||

[[Category:High Performance SoCs]] | [[Category:High Performance SoCs]] | ||

| + | [[Category:Fault Tolerance]] | ||

| + | [[Category:HW/SW Safety and Security]] | ||

[[Category:Computer Architecture]] | [[Category:Computer Architecture]] | ||

[[Category:2023]] | [[Category:2023]] | ||

[[Category:Master Thesis]] | [[Category:Master Thesis]] | ||

| − | [[Category: | + | [[Category:In progress]] |

[[Category:Lbertaccini]] | [[Category:Lbertaccini]] | ||

| + | [[Category:Michaero]] | ||

= Overview = | = Overview = | ||

| − | == Status: | + | == Status: In Progress == |

* Type: Master Thesis | * Type: Master Thesis | ||

| Line 18: | Line 21: | ||

* Supervisors: | * Supervisors: | ||

** [[:User:Lbertaccini | Luca Bertaccini]]: [mailto:lbertaccini@iis.ee.ethz.ch lbertaccini@iis.ee.ethz.ch] | ** [[:User:Lbertaccini | Luca Bertaccini]]: [mailto:lbertaccini@iis.ee.ethz.ch lbertaccini@iis.ee.ethz.ch] | ||

| + | ** [[:User:Michaero | Michael Rogenmoser]]: [mailto:michaero@iis.ee.ethz.ch michaero@iis.ee.ethz.ch] | ||

= Introduction = | = Introduction = | ||

| Line 23: | Line 27: | ||

| − | Fault-tolerant features are crucial in critical and hostile environments (automotive, space, …). The goal of this project is to enhance the | + | Fault-tolerant features are crucial in critical and hostile environments (automotive, space, …). In the PULP group, we have started developing reliable hardware designed for use in space, where high levels of radiation have a significant impact on the correctness of executions. |

| + | |||

| + | While many processing elements and memory elements have been investigated and protected, fault-tolerant floating-point units (FPUs) still need to be researched. | ||

| + | The goal of this project is to enhance the FPU developed at IIS [1] with fault-tolerant features (such as redundancy schemes [2].) For example, a fault-tolerant mode will be investigated, where multiple SIMD units inside the FPU will be used to compute the same operation; the multiple results will then be compared to detect faults. | ||

== Character == | == Character == | ||

Latest revision as of 14:23, 27 February 2024

Contents

Overview

Status: In Progress

- Type: Master Thesis

- Professor: Prof. Dr. L. Benini

- Supervisors:

Introduction

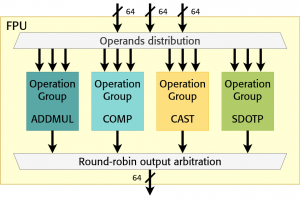

Fault-tolerant features are crucial in critical and hostile environments (automotive, space, …). In the PULP group, we have started developing reliable hardware designed for use in space, where high levels of radiation have a significant impact on the correctness of executions.

While many processing elements and memory elements have been investigated and protected, fault-tolerant floating-point units (FPUs) still need to be researched. The goal of this project is to enhance the FPU developed at IIS [1] with fault-tolerant features (such as redundancy schemes [2].) For example, a fault-tolerant mode will be investigated, where multiple SIMD units inside the FPU will be used to compute the same operation; the multiple results will then be compared to detect faults.

Character

- 20% Literature / architecture review

- 40% RTL implementation

- 40% Evaluation

Prerequisites

- Strong interest in computer architecture

- Experience with digital design in SystemVerilog as taught in VLSI I

- Experience with ASIC implementation flow (synthesis) as taught in VLSI II