Difference between revisions of "HW/SW Safety and Security"

From iis-projects

Aottaviano (talk | contribs) (→Projects In Progress) |

|||

| (7 intermediate revisions by 3 users not shown) | |||

| Line 9: | Line 9: | ||

Please continue to [[Real-Time Embedded Systems]] if you are interested in designing hardware or writing software for timing predictable embedded systems. | Please continue to [[Real-Time Embedded Systems]] if you are interested in designing hardware or writing software for timing predictable embedded systems. | ||

--> | --> | ||

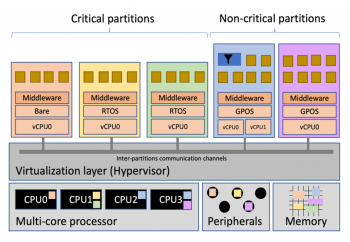

| + | [[File:Mcs.png|thumb|350px| A Mixed Criticality System (MCS).]] | ||

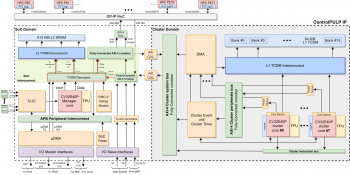

| + | [[File:Control_PULP_with_CLIC.png|thumb|350px|''Control PULP'' is a research platform for testing and implementing real-time hardware concepts. It couples a RISC-V controller core with a cluster of eight RISC-V cores used as accelerator for various control intensive applications in this case a control loop involving thermal and power capping of HPC compute cores.]] | ||

| − | A real-time computer system is a computer system in which the correctness of the system behavior depends not only on the '''logical results''' of the computations, but also on the '''physical instant''' at which these results are produced | + | A real-time computer system is a computer system in which the correctness of the system behavior depends not only on the '''logical results''' of the computations, but also on the '''physical instant''' at which these results are produced. |

| − | + | In real-time systems, guarantees must be given on the finishing of computations before a deadline. This affects the design of hardware (processors, caches, interconnects, peripherals, interrupts, ...) and software stack (operating system, scheduling, compiler guarantees). Key concepts are '''spatial and temporal isolation''' of components, and ''' architecture's predictability'''. | |

| − | + | In short, high performance systems optimize for the '''average-case''' scenario, while predictable systems optimize for '''worst-case''' scenario. | |

| + | |||

| + | One trend in real-time systems is to fuse regular low priority application code with real-time tasks on the same platform. This combination is called a '''Mixed Criticality System''' (MCS). For achieving this kind of design, various hardware and software pieces need to work together to ensure proper isolation of programs through virtualization, bandwidth partitioning, smart cahing etc. We are building such a system and offer various projects working on it. | ||

== Cryptography == | == Cryptography == | ||

| Line 50: | Line 54: | ||

* '''e-mail''': [mailto:michaero@iis.ee.ethz.ch michaero@iis.ee.ethz.ch] | * '''e-mail''': [mailto:michaero@iis.ee.ethz.ch michaero@iis.ee.ethz.ch] | ||

* '''phone''': +41 44 632 54 33 | * '''phone''': +41 44 632 54 33 | ||

| − | * '''office''': ETZ | + | * '''office''': ETZ J78 |

|} | |} | ||

| Line 56: | Line 60: | ||

| style="padding: 10px" | [[File:Nwistoff_face_pulp_team.JPG|frameless|left|96px]] | | style="padding: 10px" | [[File:Nwistoff_face_pulp_team.JPG|frameless|left|96px]] | ||

| | | | ||

| + | |||

===[[:User:Nwistoff | Nils Wistoff]]=== | ===[[:User:Nwistoff | Nils Wistoff]]=== | ||

* '''e-mail''': [mailto:nwistoff@iis.ee.ethz.ch nwistoff@iis.ee.ethz.ch] | * '''e-mail''': [mailto:nwistoff@iis.ee.ethz.ch nwistoff@iis.ee.ethz.ch] | ||

| Line 97: | Line 102: | ||

ordermethod=sortkey | ordermethod=sortkey | ||

order=ascending | order=ascending | ||

| + | </DynamicPageList> | ||

| + | <DynamicPageList> | ||

| + | category = Reserved | ||

| + | category = Digital | ||

| + | category = Fault Tolerance | ||

| + | suppresserrors=true | ||

</DynamicPageList> | </DynamicPageList> | ||

Latest revision as of 09:49, 15 January 2024

Contents

Real-Time Embedded Systems

A real-time computer system is a computer system in which the correctness of the system behavior depends not only on the logical results of the computations, but also on the physical instant at which these results are produced.

In real-time systems, guarantees must be given on the finishing of computations before a deadline. This affects the design of hardware (processors, caches, interconnects, peripherals, interrupts, ...) and software stack (operating system, scheduling, compiler guarantees). Key concepts are spatial and temporal isolation of components, and architecture's predictability.

In short, high performance systems optimize for the average-case scenario, while predictable systems optimize for worst-case scenario.

One trend in real-time systems is to fuse regular low priority application code with real-time tasks on the same platform. This combination is called a Mixed Criticality System (MCS). For achieving this kind of design, various hardware and software pieces need to work together to ensure proper isolation of programs through virtualization, bandwidth partitioning, smart cahing etc. We are building such a system and offer various projects working on it.

Cryptography

Please continue to Cryptography if you are interested in cryptographic hardware.

Fault Tolerance

Please continue to Fault Tolerance if you are interested in circuits tolerant to radiation-induced soft errors.

Who are we

Robert Balas

|

Alessandro Ottaviano

|

Michael Rogenmoser

|

Nils Wistoff

|

Projects

All projects are annotated with one or more possible project types (M/S/B/G) and a number of students (1 to 3).

- M: Master's thesis: 26 weeks full-time (6 months) for one student only

- S: Semester project: 14 weeks half-time (1 semester lecture period) or 7 weeks full-time for 1-3 students

- B: Bachelor's thesis: 14 weeks half-time (1 semester lecture period) for one student only

- G: Group project: 14 weeks part-time (1 semester lecture period) for 2-3 students

Usually, these are merely suggestions from our side; proposals can often be reformulated to fit students' needs.

Available Projects

- Designing a Fault-Tolerant On-Chip Interconnect (1-2S/M)

- Enhancing our DMA Engine with Fault Tolerance

- Fast Accelerator Context Switch for PULP

- FPGA mapping of RPC DRAM

- Non-blocking Algorithms in Real-Time Operating Systems

- PULP Freertos with LLVM

- Resource Partitioning of RPC DRAM

- Scan Chain Fault Injection in a PULP SoC (1S)

- Securing Block Ciphers against SCA and SIFA

Projects In Progress

- A RISC-V fault-tolerant many-core accelerator for 5G Non-Terrestrial Networks (1-2S/B)

- Fault-Tolerant Floating-Point Units (M)

- Implementation of a Cache Reliability Mechanism (1S/M)

- On-Board Software for PULP on a Satellite

- Radiation Testing of a PULP ASIC

- Zephyr RTOS on PULP

Completed Projects

- Resource Partitioning of Caches

- Design of an Area-Optimized Soft-Error Resilient Processing Core for Safety-Critical Systems (1M)

- Development of statistics and contention monitoring unit for PULP

- Implementing Configurable Dual-Core Redundancy

- Peripheral Event Linking System for Real-time Capable Energy Efficient SoCs

- CLIC for the CVA6

- SCMI Support for Power Controller Subsystem

- PULP’s CLIC extensions for fast interrupt handling

- Triple-Core PULPissimo

- Watchdog Timer for PULP

- Hypervisor Extension for Ariane (M)

- Securing Block Ciphers against SCA and SIFA