Difference between revisions of "High Performance Digitally-Assisted Time Domain ADC Design for DPLL used in Cellular IOT"

From iis-projects

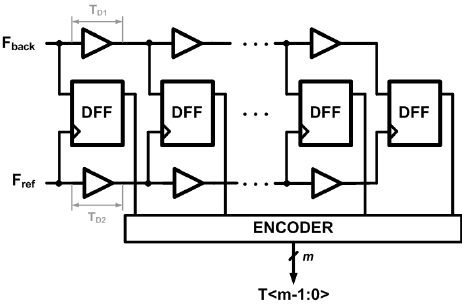

(Created page with "thumb|600px|Typical Vernier Delay Line based TDC (Time to Digital Convertor) ==Short Description== Tough frequency synthesize require...") |

(No difference)

|

Revision as of 13:28, 20 September 2016

Contents

Short Description

Tough frequency synthesize requirement imposed by cellular applications have been a key driver for PLL research in recent years. As the age of cellular internet of things is coming, motivation for designing power efficient PLL (supreme phase noise performance at low power) is getting stronger than ever. Locating at the heart of PLL, VCO does not only determine the phase noise performance of PLL (especially far out part) but also contributes considerably to the total power budget. As the result, stringent design specifications provide considerable incentive for research solely focused on improving the voltage-controlled oscillator (VCO) performance, one of the most challenging aspects of PLL design. The aim of this project is to analyze and build such a power efficient sub-10 mW Digital controlled Oscillator (DCO) for GHz frequency range, to achieve a state-of-art performance, finally leading the way to a low power low jitter Digital PLL.

Status: Available

- Looking for 1-2 Semester students

- Contact: Lianbo Wu

Prerequisites

- AIC

Character

- 30% Theory

- 70% Circuit Design