Difference between revisions of "High Performance Digitally-Assisted Time Domain ADC Design for DPLL used in Cellular IOT"

From iis-projects

| Line 46: | Line 46: | ||

==Links== | ==Links== | ||

| − | # R. B. Staszewski and P. T. Balsara, All-Digital Frequency Synthesizer in Deep-Submicron CMOS, New Jersey: John Wiley & Sons, Inc., 261 pages, ISBN: 978-0471772552, Sept. 2006. DOI: 10.1002/9780470041956. | + | # R. B. Staszewski and P. T. Balsara, "All-Digital Frequency Synthesizer in Deep-Submicron CMOS", New Jersey: John Wiley & Sons, Inc., 261 pages, ISBN: 978-0471772552, Sept. 2006. DOI: 10.1002/9780470041956. |

[[Category:Analog]] | [[Category:Analog]] | ||

[[Category:Available]] | [[Category:Available]] | ||

Revision as of 13:56, 20 September 2016

Contents

Short Description

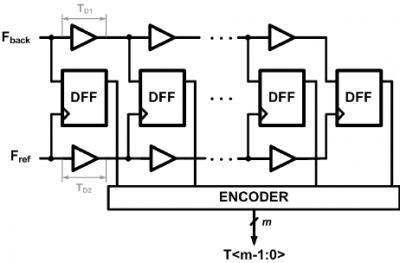

As CMOS process node is progressing towards quantum level, voltage headroom is reduced correspondingly while transistor speed is increased on the other hand. Therefore, it is time to use time, indicating that it is beneficial to incorporate signal information into time domain rather than conventional analog voltage domain. This gives the birth of phase domain Digital PLL and thus the emerging of time domain ADC. Compared with its mature analog counterpart topic (Phase/Frequency Detector+ Charge Pump), concept of ADC is leveraged into DPLL to quantize analog phase /frequency error in time domain. This topic is drawing more and more attention over the past 5 years as seen in numerous top publications and patents. Highly digitally-assisted analog design is the trend for time domain ADC, such as DTC+TDC, Bang-Bang Detector. Following such a trend, the aim of this project is to analyze and build a time domain ADC innovatively so that the in-band jitter contribution of the DPLL could be lower than 500fs while consuming power less than 1 mW.

Status: Available

- Looking for 1-2 Semester students

- Contact: Lianbo Wu

Prerequisites

- AIC

Character

- 30% Theory

- 70% Circuit Design

Professor

Detailed Task Description

Goals

Practical Details

Results

Links

- R. B. Staszewski and P. T. Balsara, "All-Digital Frequency Synthesizer in Deep-Submicron CMOS", New Jersey: John Wiley & Sons, Inc., 261 pages, ISBN: 978-0471772552, Sept. 2006. DOI: 10.1002/9780470041956.↑ top