Difference between revisions of "Hybrid Analog/Digital Leveling Loop for Very-Low-Distortion Oscillator"

From iis-projects

| Line 36: | Line 36: | ||

[[Category:Semester Thesis]] | [[Category:Semester Thesis]] | ||

[[Category:Audio]] | [[Category:Audio]] | ||

| + | [[Category:Felber]] | ||

<!-- | <!-- | ||

Latest revision as of 20:06, 17 February 2015

Contents

Short Description

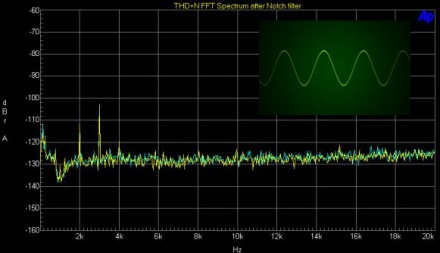

A key quality parameter of audio signal paths is their distortion performance. For distortion measurements, an oscillator with very low harmonic content (i.e. itself has very low distortion) and noise is necessary. For state-of-the-art resolution, fully analog RC oscillators are required. To stabilize their amplitude, a leveling loop consisting of level detector, error integrator and a multiplier is employed. Implementation of this leveling loop is critical to oscillator performance (e.g. it affects harmonic distortion, settling time and sideband noise) and poses several demanding tradeoffs. This semester thesis investigates a hybride implementation, where the signal path of the leveling loop comprises an AD converter and a multiplying DA converter, with intermediate digital signal processing (FPGA or DSP). Carried out with an industry partner (Weiss Engineering Ltd.).

Status: Available

- Looking for 1-2 Semester students

- Contact: Norbert Felber

Prerequisites

- Interest in high-performance mixed signal circuit design;

- Background in hardware design and low-level sofware implementation (e.g. VHDL or assembler) beneficial

Character

- 70% Hardware Implementation

- 30% Software Implementation