Difference between revisions of "VLSI Design of an Asynchronous LDPC Decoder"

From iis-projects

| Line 2: | Line 2: | ||

==Short Description== | ==Short Description== | ||

| − | Virtually all modern digital VLSI designs are synchronous due to the availability of easy-to-use electronic design automation (EDA) software that significantly facilitates circuit design. The main drawback of synchronous designs, however, is the fact that the worst propagation delay (the critical path) determines the global operation frequency, whereas large parts of most designs could run at significantly faster rates. In stark contrast, asynchronous digital VLSI circuits do not rely on a global clock and enable one to operate each part of a design at the fastest possible rate. This design paradigm | + | Virtually all modern digital VLSI designs are synchronous due to the availability of easy-to-use electronic design automation (EDA) software that significantly facilitates circuit design. The main drawback of synchronous designs, however, is the fact that the worst propagation delay (the critical path) determines the global operation frequency, whereas large parts of most designs could run at significantly faster rates. In stark contrast, asynchronous digital VLSI circuits do not rely on a global clock and enable one to operate each part of a design at the fastest possible rate. This design paradigm has the potential to enable significantly higher throughput or reduced power consumption compared to synchronous circuits. While asynchronous logic has blatant advantages over synchronous designs, asynchronous VLSI design was, up until now, not supported by EDA tools and, hence, enjoyed only limited use in practice. |

The goal of this project is to use a recently developed open-source EDA tool-flow for asynchronous VLSI design developed at Yale University [1], in order to design, implement, and fabricate a low-density parity check (LDPC) decoder for fifth-generation (5G) wireless communication systems. The project will proceed in three stages: First, the student(s) will modify conventional, synchronous message-passing algorithms for LDPC decoding to enable asynchronous message passing. Second, the student(s) will design and implement the asynchronous decoding algorithm using the open-source EDA tools available at [2]. Third, the student(s) will compare their asynchronous design to state-of-the-art synchronous LDPC decoders in the same process technology. | The goal of this project is to use a recently developed open-source EDA tool-flow for asynchronous VLSI design developed at Yale University [1], in order to design, implement, and fabricate a low-density parity check (LDPC) decoder for fifth-generation (5G) wireless communication systems. The project will proceed in three stages: First, the student(s) will modify conventional, synchronous message-passing algorithms for LDPC decoding to enable asynchronous message passing. Second, the student(s) will design and implement the asynchronous decoding algorithm using the open-source EDA tools available at [2]. Third, the student(s) will compare their asynchronous design to state-of-the-art synchronous LDPC decoders in the same process technology. | ||

Latest revision as of 17:36, 20 October 2021

Contents

Short Description

Virtually all modern digital VLSI designs are synchronous due to the availability of easy-to-use electronic design automation (EDA) software that significantly facilitates circuit design. The main drawback of synchronous designs, however, is the fact that the worst propagation delay (the critical path) determines the global operation frequency, whereas large parts of most designs could run at significantly faster rates. In stark contrast, asynchronous digital VLSI circuits do not rely on a global clock and enable one to operate each part of a design at the fastest possible rate. This design paradigm has the potential to enable significantly higher throughput or reduced power consumption compared to synchronous circuits. While asynchronous logic has blatant advantages over synchronous designs, asynchronous VLSI design was, up until now, not supported by EDA tools and, hence, enjoyed only limited use in practice.

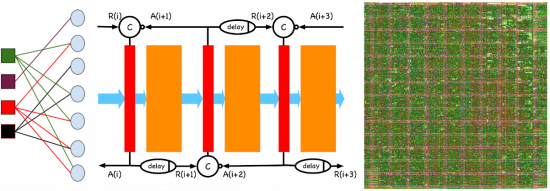

The goal of this project is to use a recently developed open-source EDA tool-flow for asynchronous VLSI design developed at Yale University [1], in order to design, implement, and fabricate a low-density parity check (LDPC) decoder for fifth-generation (5G) wireless communication systems. The project will proceed in three stages: First, the student(s) will modify conventional, synchronous message-passing algorithms for LDPC decoding to enable asynchronous message passing. Second, the student(s) will design and implement the asynchronous decoding algorithm using the open-source EDA tools available at [2]. Third, the student(s) will compare their asynchronous design to state-of-the-art synchronous LDPC decoders in the same process technology.

In order to facilitate VLSI design with these experimental EDA tools [2,3], called ACT (short for Asynchronous Circuit Toolkit), the project will be co-advised by the Yale Asynchronous VLSI and Architecture Group led by Prof. Rajit Manohar.

[1] S. Ataei et al., “An Open-Source EDA Flow for Asynchronous Logic,” IEEE Design & Test, Vol. 38, No. 2, Apr. 2021

[2] https://github.com/asyncvlsi/

[3] https://avlsi.csl.yale.edu/act/doku.php

Status: Available

- Looking for 1-2 Semester/Bachelor/Master students

- Contact: Christoph Studer

Prerequisites

- Communication Systems (or a similar course)

- VLSI 1

- VLSI 3 (recommended)

Character

- 50% Algorithm development in MATLAB

- 50% Asynchronous VLSI design with ACT