Novel Metastability Mitigation Technique

From iis-projects

Contents

Description

Modern system-on-a-chip is usually an integration of heterogeneous building blocks. Such heterogeneous systems typically have multiple power and clock domains. Therefore, it is critical to ensure robustness when data cross different power and clock domains.

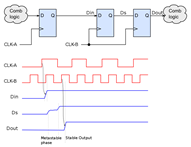

Metastability happens when the input signal changes within the setup-hold window around the latching clock. As a result, the circuit persists in an unstable equilibrium in metastability, which influences the correctness of the data and the power consumption.

The synchronizer is an effective and commonly used method against metastability, but it does not ensure the correctness of the data. In this project, the student will explore a novel approach that employs passive devices to mitigate the metastability issue.

Status: In progress

- Looking for master or semester thesis students

- Supervisor: Giorgio Cristiano, Jiawei Liao

Prerequisites

- VLSI

- AIC

Character

- 20% Literature review

- 20% Theory

- 60% Design and simulation

Professor

Prof. Taekwang Jang <tjang@ethz.ch>