Writing a Hero runtime for EPAC (1-3S/B)

From iis-projects

Contents

Overview

Status: Reserved

- Type: Computer Architecture Bachelor / Semester Thesis

- Professor: Prof. Dr. L. Benini

- Supervisors:

Introduction

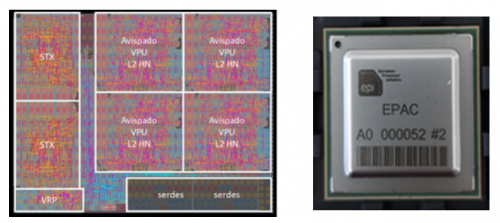

EPAC is one of the chip resulting from the European Processor Initiative (EPI) consortium, in which ETH Zurich is involved. The EPAC and EPAC1.5 chips have been successfully taped-out in the past years and are available at IIS for testing and developing SW. This heterogeneous chip contains four RISC-V Avispado cores along with two STX accelerator tiles and one Variable floating point precision core.

Source: [1]

Source: [1]

OpenMP is an Application Programming Interface (API) that supports multi-platform shared-memory multiprocessing programming in C, C++, and Fortran. OpenMP allows developers to write parallel programs that can run on a wide range of hardware, including multi-core processors and symmetric multiprocessing (SMP) systems. OpenMP uses pragma directives to exploit parallelism in the annotated code regions. These directives are embedded in the source code and guide the compiler in generating parallel executable code. In addition to compiler support, an OpenMP runtime library abstracts the details of thread creation and management from the programmer, simplifying the parallelization process.

Starting from version 4.0, OpenMP introduced a target directive, which allows offloading computations to accelerators by explicitly specifying the code regions amenable to execute on the accelerator.

int main() {

printf("Hello from the host\n");

#pragma omp target device(1)

{

printf("Hello from the accelerator main thread\n");

#pragma omp parallel

printf("Hello from the accelerator thread %i\n", omp_get_thread_num());

}

}

The HERO stack, developed at IIS, proposes an implementation of the OpenMP runtime that can run on multiple of our SoCs with a maximum of code reuse.

Project

This project aims to port the HERO stack to the EPAC1.5 chip in order to benchmark multiple OpenMP based kernel and applications on this state of the art Heterogeneous SoC.

In order to reach this goal, the student will have to familiarize with the EPAC1.5 chip architecture and it's interface (the chip is programmable via a FPGA host setup). The student will then need to understand the HERO runtime and port it to EPAC. Finally they will implement some benchmarks or applications using OpenMP targeting the accelerators inside the chip.

Character

- 20% Get familiar with the SoC architecture and its progrmaming interface

- 20% Study the Hero runtimes

- 40% Propose and implement the runtime plugin (written in C) for EPAC

- 20% Benchmark some OpenMP kernel on the STX accelerator

Prerequisites

- Good knowledge of computer architectures

- Proficient in C, knowledge of C++

- Willing to learn about Linux and Linux drivers