Difference between revisions of "Energy Efficient Circuits and IoT Systems Group"

From iis-projects

(Created page with "test") |

|||

| Line 1: | Line 1: | ||

| − | + | __NOTOC__ | |

| + | <imagemap> | ||

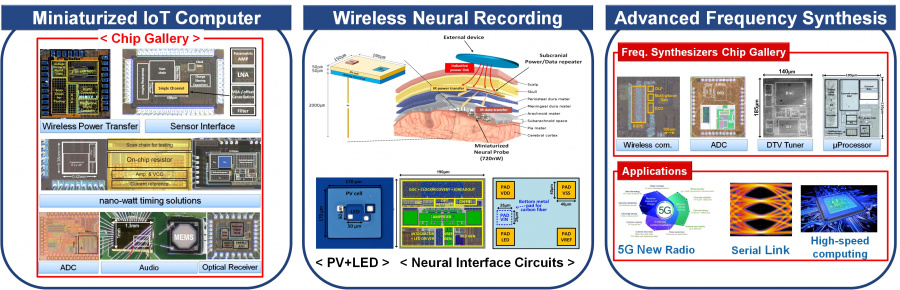

| + | Image:Project_outline.jpg|900px | ||

| + | rect 0 1101 1125 0 [[Design of key building blocks for miniaturized sensor systems]] | ||

| + | rect 1140 1101 2255 0 [[Energy Efficient Circuits for Wireless Neural Recording]] | ||

| + | rect 2278 1101 3418 0 [[Application Specific Frequency Synthesizers (Analog/Digital PLLs)]] | ||

| + | default [[Energy Efficient Circuits and IoT Systems Group]] | ||

| + | desc none | ||

| + | </imagemap> | ||

| + | |||

| + | ==Available Projects== | ||

| + | <DynamicPageList> | ||

| + | suppresserrors = true | ||

| + | category = Available | ||

| + | category = EECIS | ||

| + | </DynamicPageList> | ||

| + | |||

| + | ==Active Projects== | ||

| + | <DynamicPageList> | ||

| + | suppresserrors = true | ||

| + | category = In progress | ||

| + | category = EECIS | ||

| + | </DynamicPageList> | ||

| + | <DynamicPageList> | ||

| + | suppresserrors = true | ||

| + | category = In progress | ||

| + | category = Telecommunications | ||

| + | </DynamicPageList> | ||

| + | |||

| + | ==Completed Projects== | ||

Revision as of 15:24, 25 September 2019

Available Projects

- Neural Recording Interface and Spike Sorting Algorithm

- Energy-Efficient Edge-Pursuit comparator for ultra-low power ADC

- Design of Streaming Data Platform for High-Speed ADC Data

- Design of Power-Noise-Efficient Discrete-Time Amplifier Using Open-Source Tools

- An Ultra-Low-Power Neuromorphic Spiking Neuron Design

- Energy Efficient Serial Link

- Design of low mismatch DAC used for VAD

- Development of an implantable Force sensor for orthopedic applications

- Energy-efficient Circuits for Fully Wireless Brain-machine Interfaces

- Design of Time-Encoded Spiking Neural Networks (IBM-Zurich)

- Spiking Neural Network for Motor Function Decoding Based on Neural Dust

- Hardware/software codesign neural decoding algorithm for “neural dust”

- Exploring feature selection and classification algorithms for ultra-low-power closed-loop systems for epilepsy control

- Application Specific Frequency Synthesizers (Analog/Digital PLLs)

Active Projects

- ASIC Development of 5G-NR LDPC Decoder

- Channel Estimation for 5G Cellular IoT and Fast Fading Channels