Design of Power-Noise-Efficient Discrete-Time Amplifier Using Open-Source Tools

From iis-projects

Contents

Description

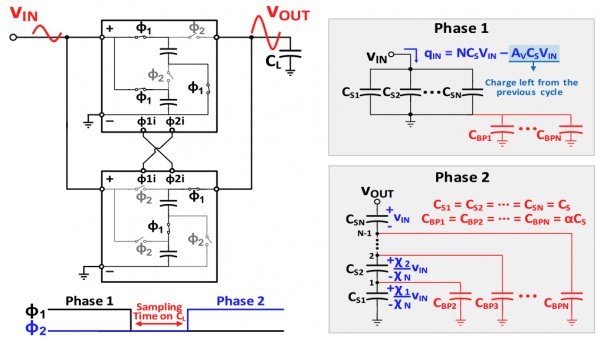

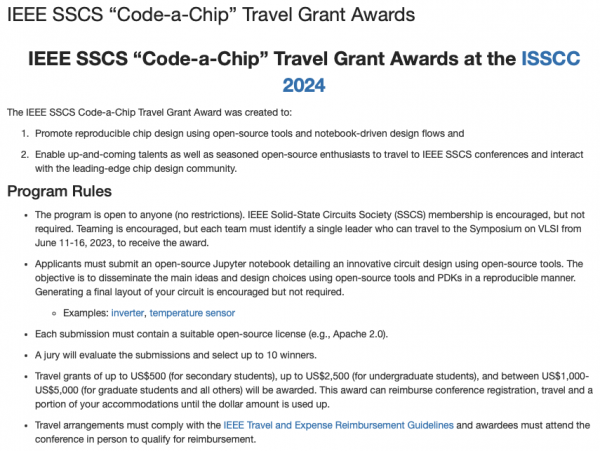

Energy-Efficient Circuits and Intelligent Systems (EECIS) Group recently presented an ultra-noise-efficient amplifier design using switched-capacitor circuits [1-3]. In this project, you will 1) explore replicating the same design based on open-source circuit design tools, and 2) seek to further improve the existing low-noise amplifier circuit. The designed circuit will be simulated for the performance verifications. If the design result is promising, you can target and try to submit your open-source design to the 'Code-a-Chip' travel grant, sponsored by the Solid-State Circuit Society (SSCS). The selected code-a-chip open-source design will be granted travel fees to attend the most prestigious and unrivaled circuit design conference, the International Solid-State Circuit Conference (ISSCC). If selected, this opportunity will elevate your personal record to an exceptionally higher level than other master students, having both 1) circuit design experience and 2) SSCS-sponsored award.

- Looking for master or semester thesis students

- Supervisor: Kwantae Kim <kimkwa@ethz.ch>

Prerequisites

- Python

- Analog Integrated Circuits

Character

- 20% Literature review

- 20% Open-source tool usage

- 60% Circuit design

Professor

Prof. Taekwang Jang <tjang@ethz.ch>

Reference

[1] G. Atzeni, A. Novello, G. Cristiano, J. Liao and T. Jang, "A 0.45/0.2-NEF/PEF 12-nV/√Hz Highly Configurable Discrete-Time Low-Noise Amplifier," in IEEE Solid-State Circuits Letters, vol. 3, pp. 486-489, 2020, doi: 10.1109/LSSC.2020.3029016.

[2] G. Atzeni et al., "An Impedance-boosted Switched-capacitor Low-noise Amplifier Achieving 0.4 NEF," 2022 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits), Honolulu, HI, USA, 2022, pp. 116-117, doi: 10.1109/VLSITechnologyandCir46769.2022.9830399.

[3] G. Atzeni, C. Livanelioglu, L. Recchioni, S. Arjmandpour and T. Jang, "An Energy-Efficient Impedance-Boosted Discrete-Time Amplifier Achieving 0.34 Noise Efficiency Factor and 389 MΩ Input Impedance," 2023 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits), Kyoto, Japan, 2023, pp. 1-2, doi: 10.23919/VLSITechnologyandCir57934.2023.10185212.