Difference between revisions of "An Ultra-Low-Power Neuromorphic Spiking Neuron Design"

From iis-projects

(→Status: To be Available) |

(→Status: Available) |

||

| (11 intermediate revisions by the same user not shown) | |||

| Line 1: | Line 1: | ||

| − | [[File: | + | [[File:KwantaeKim_2023-10-20_at_16.51.08.png|thumb|600px]] |

=== Description === | === Description === | ||

| − | Integrate-and-Fire (IAF) neurons are widely available in neuromorphic spike-processing applications. | + | Integrate-and-Fire (IAF) neurons are widely available in neuromorphic spike-processing applications. Analog LIF neurons are considered a breakthrough to realize fully analog, fully asynchronous spiking neural network implementation for ultra-low-power AI-embedded systems. In this project, you will seek to realize an analog ultra-low-power (thus low energy/spike) LIF neuron, having a very low-frequency spiking rate (e.g., <100Hz). The prerequisite course is Analog integrated circuits. If the design result is promising, the study will be summarized and submitted to IEEE conferences such as ISCAS/BioCAS. |

| − | ===Status: | + | ===Status: Unavailable=== |

:Looking for master or semester thesis students | :Looking for master or semester thesis students | ||

:Supervisor: [[:User:Kimkwa | Kwantae Kim]] <[mailto:kimkwa@ethz.ch kimkwa@ethz.ch]> | :Supervisor: [[:User:Kimkwa | Kwantae Kim]] <[mailto:kimkwa@ethz.ch kimkwa@ethz.ch]> | ||

===Prerequisites=== | ===Prerequisites=== | ||

| − | * Analog | + | * Analog integrated circuits |

===Character=== | ===Character=== | ||

| Line 18: | Line 18: | ||

Prof. Taekwang Jang <[mailto:tjang@ethz.ch tjang@ethz.ch]> | Prof. Taekwang Jang <[mailto:tjang@ethz.ch tjang@ethz.ch]> | ||

=== Reference=== | === Reference=== | ||

| − | [1] | + | [1] S. Kim, S. Kim, S. Um, S. Kim, K. Kim and H. -J. Yoo, "Neuro-CIM: ADC-Less Neuromorphic Computing-in-Memory Processor With Operation Gating/Stopping and Digital–Analog Networks," in IEEE Journal of Solid-State Circuits, vol. 58, no. 10, pp. 2931-2945, Oct. 2023, doi: 10.1109/JSSC.2023.3273238. |

| + | |||

| + | [2] A. Rubino, C. Livanelioglu, N. Qiao, M. Payvand and G. Indiveri, "Ultra-Low-Power FDSOI Neural Circuits for Extreme-Edge Neuromorphic Intelligence," in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 68, no. 1, pp. 45-56, Jan. 2021, doi: 10.1109/TCSI.2020.3035575. | ||

| + | |||

| + | [3] S. Vuppunuthala and V. S. Pasupureddi, "3.6-pJ/Spike, 30-Hz Silicon Neuron Circuit in 0.5-V, 65 nm CMOS for Spiking Neural Networks," in IEEE Transactions on Circuits and Systems II: Express Briefs, doi: 10.1109/TCSII.2023.3324584. | ||

| + | |||

[[#top|↑ top]] | [[#top|↑ top]] | ||

[[Category:EECIS]] | [[Category:EECIS]] | ||

[[Category:Available]] | [[Category:Available]] | ||

| − | [[Category: | + | [[Category:2023]] |

[[Category:Kimkwa]] | [[Category:Kimkwa]] | ||

[[Category:Semester Thesis]] | [[Category:Semester Thesis]] | ||

Latest revision as of 17:01, 4 March 2024

Contents

Description

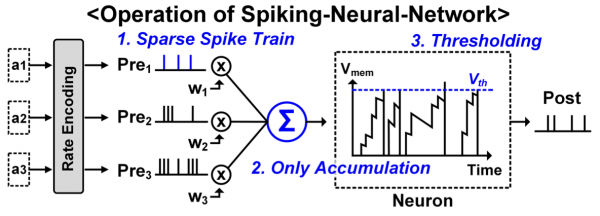

Integrate-and-Fire (IAF) neurons are widely available in neuromorphic spike-processing applications. Analog LIF neurons are considered a breakthrough to realize fully analog, fully asynchronous spiking neural network implementation for ultra-low-power AI-embedded systems. In this project, you will seek to realize an analog ultra-low-power (thus low energy/spike) LIF neuron, having a very low-frequency spiking rate (e.g., <100Hz). The prerequisite course is Analog integrated circuits. If the design result is promising, the study will be summarized and submitted to IEEE conferences such as ISCAS/BioCAS.

- Looking for master or semester thesis students

- Supervisor: Kwantae Kim <kimkwa@ethz.ch>

Prerequisites

- Analog integrated circuits

Character

- 20% Literature review

- 20% Theory

- 60% Circuit Design

Professor

Prof. Taekwang Jang <tjang@ethz.ch>

Reference

[1] S. Kim, S. Kim, S. Um, S. Kim, K. Kim and H. -J. Yoo, "Neuro-CIM: ADC-Less Neuromorphic Computing-in-Memory Processor With Operation Gating/Stopping and Digital–Analog Networks," in IEEE Journal of Solid-State Circuits, vol. 58, no. 10, pp. 2931-2945, Oct. 2023, doi: 10.1109/JSSC.2023.3273238.

[2] A. Rubino, C. Livanelioglu, N. Qiao, M. Payvand and G. Indiveri, "Ultra-Low-Power FDSOI Neural Circuits for Extreme-Edge Neuromorphic Intelligence," in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 68, no. 1, pp. 45-56, Jan. 2021, doi: 10.1109/TCSI.2020.3035575.

[3] S. Vuppunuthala and V. S. Pasupureddi, "3.6-pJ/Spike, 30-Hz Silicon Neuron Circuit in 0.5-V, 65 nm CMOS for Spiking Neural Networks," in IEEE Transactions on Circuits and Systems II: Express Briefs, doi: 10.1109/TCSII.2023.3324584.