Difference between revisions of "DMA Streaming Co-processor"

From iis-projects

| Line 1: | Line 1: | ||

| + | ==Short Description== | ||

| + | [[File:Ap signals.png|400px|thumb|right|Sample Preprocessing]] | ||

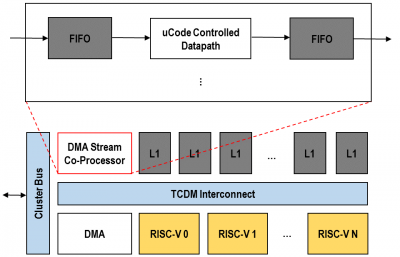

[[File:StreamingProc.png|thumb|400px|The streaming processor would act as a co-processor for the DMA in the PULP cluster.]] | [[File:StreamingProc.png|thumb|400px|The streaming processor would act as a co-processor for the DMA in the PULP cluster.]] | ||

| − | |||

| − | |||

In many cases a lot of resources are consumed during a preprocessing phase in which the raw data coming, e.g., from an image sensor is transformed in a proper way before being fed to the main processing algorithms. This preprocessing, in many cases, could be done very efficiently while moving the data through the memory hierarchy (e.g. L2 -> L1 transfers). | In many cases a lot of resources are consumed during a preprocessing phase in which the raw data coming, e.g., from an image sensor is transformed in a proper way before being fed to the main processing algorithms. This preprocessing, in many cases, could be done very efficiently while moving the data through the memory hierarchy (e.g. L2 -> L1 transfers). | ||

Revision as of 19:28, 14 April 2016

Contents

Short Description

In many cases a lot of resources are consumed during a preprocessing phase in which the raw data coming, e.g., from an image sensor is transformed in a proper way before being fed to the main processing algorithms. This preprocessing, in many cases, could be done very efficiently while moving the data through the memory hierarchy (e.g. L2 -> L1 transfers).

Like other processors, the PULP platform provides a standard DMA controller for efficient data transfers. In this work, we are going to design a streaming co-processor for the DMA with limited programmability. This co-processor could then perform such tasks on-the-fly when the data is being copied.

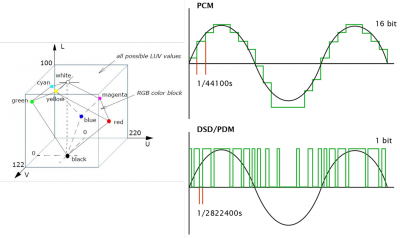

Potential application candidates include signal filtering for audio/motion sensor, sub/over sampling, color scheme conversion, image filtering, ciphering and compression/decompression.

Status: Available

- Scope: Semester or Master Thesis

- Looking for 1-2 Interested Students

- Supervisors: Michael Schaffner, Michael Gautschi, Antonio Pullini

Prerequisites

- VLSI I

- Basic Computer Architecture Course

- Matlab, VHDL and C++

Character

- 10% Theory & Literature Study

- 20% Evaluations

- 70% Hw Architecture & ASIC Implementation