Difference between revisions of "High performance continuous-time Delta-Sigma ADC for magnetic resonance imaging"

From iis-projects

(Created page with "thumb|400px ==Short Description== Acquisition of physiological signals to establish health status or to investigate...") |

|||

| Line 1: | Line 1: | ||

[[File: Continuous Time Delta-Sigma Converter Breems.png|thumb|400px]] | [[File: Continuous Time Delta-Sigma Converter Breems.png|thumb|400px]] | ||

==Short Description== | ==Short Description== | ||

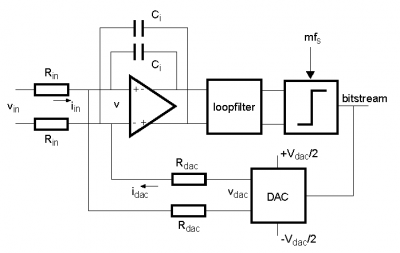

| − | + | Delta-sigma based converters have been the topology of choice for mobile communications application since several years due to their high dynamic range and high linearity. More recently the main implementation technique has changed from discrete-time switched capacitor to continuous-time, RC based structures, because they offer implicit filtering, do not need as much buffering in front and can be realized with less power consumption. In this thesis a continuous-time delta-sigma modulator for up to 25MHz bandwidth and 68dB SNDR will be investigated first at behavioral level, followed by a circuit design in 130nm CMOS. It will be possible to learn the whole the design cycle including system simulation and layout as a master student. | |

===Status: Available === | ===Status: Available === | ||

| − | : Looking for 1-2 | + | : Looking for 1-2 Master students |

: Contact: [[:User:Burger | Thomas Burger]] | : Contact: [[:User:Burger | Thomas Burger]] | ||

===Prerequisites=== | ===Prerequisites=== | ||

Revision as of 16:16, 8 May 2017

Contents

Short Description

Delta-sigma based converters have been the topology of choice for mobile communications application since several years due to their high dynamic range and high linearity. More recently the main implementation technique has changed from discrete-time switched capacitor to continuous-time, RC based structures, because they offer implicit filtering, do not need as much buffering in front and can be realized with less power consumption. In this thesis a continuous-time delta-sigma modulator for up to 25MHz bandwidth and 68dB SNDR will be investigated first at behavioral level, followed by a circuit design in 130nm CMOS. It will be possible to learn the whole the design cycle including system simulation and layout as a master student.

Status: Available

- Looking for 1-2 Master students

- Contact: Thomas Burger

Prerequisites

- AIC

Character

- 30% Theory

- 20% System Simulation (Matlab/Simulink)

- 50% Circuit Design