Difference between revisions of "NextGenChannelDec"

From iis-projects

(Created page with "thumb|400px|Channel Decoder in Today's Communication Systems ==Short Description== Today, Turbo Decoder and LDPC Decoder are well establishe...") |

|||

| Line 1: | Line 1: | ||

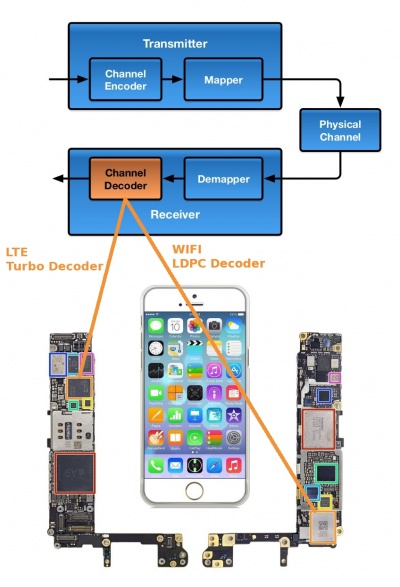

[[File:channel_decoder_intro.jpg|thumb|400px|Channel Decoder in Today's Communication Systems]] | [[File:channel_decoder_intro.jpg|thumb|400px|Channel Decoder in Today's Communication Systems]] | ||

==Short Description== | ==Short Description== | ||

| − | Today, Turbo Decoder and LDPC Decoder are well established in the majority of communication systems. While the physical baseband computation in the cellular LTE standard for example | + | Today, Turbo Decoder and LDPC Decoder are well established in the majority of communication systems. While the physical baseband computation in the cellular LTE standard bases for example on Turbo codes, LDPC codes have been adopted in the Wifi standard IEEE802.11n/ac/ax. With that the question arises: What comes next? |

| − | |||

| − | + | There are various channel decoding algorithms which could potentially succeed Turbo and LDPC codes. Promising candidates are: Non-binary LDPC codes, Spatially-Coupled LDPC Codes, and Polar Codes. The goal of this project is to do a quantitative evaluation of the channel decoding candidates based on optimized VLSI implementations. | |

| − | + | Your first task in this project will be to develop a hardware-friendly decoder architecture for one of the channel decoder candidates. After porting the decoder architecture to HDL, an ASIC implementation will be derived by logic synthesis of the developed RTL code. The work concludes with a comparison of the generated ASIC with literature and especially with implementations of other channel decoder candidates. | |

| + | |||

| + | In case a Master Thesis is pursued, one further task will be to optimize the selected fix-point decoding algorithm towards a VLSI implementation. | ||

===Status: Available === | ===Status: Available === | ||

| Line 27: | Line 28: | ||

---> | ---> | ||

===Character=== | ===Character=== | ||

| − | : | + | : 30% Theory, Algorithms, and Simulation |

: 30% Architectural Design | : 30% Architectural Design | ||

| − | : | + | : 40% HDL Implementation |

===Professor=== | ===Professor=== | ||

| Line 55: | Line 56: | ||

[[Category:Digital]] | [[Category:Digital]] | ||

[[Category:Master Thesis]] | [[Category:Master Thesis]] | ||

| + | [[Category:Semester Thesis]] | ||

[[Category:Available]] | [[Category:Available]] | ||

[[Category:Hot]] | [[Category:Hot]] | ||

| − | |||

[[Category:ASIC]] | [[Category:ASIC]] | ||

[[Category:Telecommunications]] | [[Category:Telecommunications]] | ||

[[Category:Mkorb]] | [[Category:Mkorb]] | ||

| − | |||

<!-- | <!-- | ||

Revision as of 15:25, 13 April 2016

Short Description

Today, Turbo Decoder and LDPC Decoder are well established in the majority of communication systems. While the physical baseband computation in the cellular LTE standard bases for example on Turbo codes, LDPC codes have been adopted in the Wifi standard IEEE802.11n/ac/ax. With that the question arises: What comes next?

There are various channel decoding algorithms which could potentially succeed Turbo and LDPC codes. Promising candidates are: Non-binary LDPC codes, Spatially-Coupled LDPC Codes, and Polar Codes. The goal of this project is to do a quantitative evaluation of the channel decoding candidates based on optimized VLSI implementations.

Your first task in this project will be to develop a hardware-friendly decoder architecture for one of the channel decoder candidates. After porting the decoder architecture to HDL, an ASIC implementation will be derived by logic synthesis of the developed RTL code. The work concludes with a comparison of the generated ASIC with literature and especially with implementations of other channel decoder candidates.

In case a Master Thesis is pursued, one further task will be to optimize the selected fix-point decoding algorithm towards a VLSI implementation.

Status: Available

- Looking for Interested Master Students (Semester Project / Master Thesis)

- Contact: Matthias Korb

Prerequisites

- VLSI I

Character

- 30% Theory, Algorithms, and Simulation

- 30% Architectural Design

- 40% HDL Implementation