Difference between revisions of "Optimal routing for 2D Mesh-based Analog Compute-In-Memory Accelerator Architecture (IBM-Zurich)"

From iis-projects

| Line 1: | Line 1: | ||

| − | [[File:optimal_routing_for_ACiM.png|thumb| | + | [[File:optimal_routing_for_ACiM.png|thumb|1200px]] |

=== Description === | === Description === | ||

The explosive application of deep neural networks to every conceivable domain has led to a consequent interest in acceleration architectures for performing efficient inference of very large networks. While GPUs remain the leading device of choice for DNN implementation, more exotic accelerators including dedicated ASIC designs and in-memory based designs have also been proposed. | The explosive application of deep neural networks to every conceivable domain has led to a consequent interest in acceleration architectures for performing efficient inference of very large networks. While GPUs remain the leading device of choice for DNN implementation, more exotic accelerators including dedicated ASIC designs and in-memory based designs have also been proposed. | ||

Revision as of 12:15, 29 July 2023

Contents

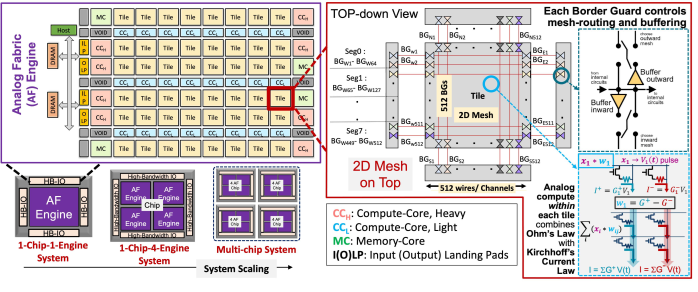

Description

The explosive application of deep neural networks to every conceivable domain has led to a consequent interest in acceleration architectures for performing efficient inference of very large networks. While GPUs remain the leading device of choice for DNN implementation, more exotic accelerators including dedicated ASIC designs and in-memory based designs have also been proposed. In this regard, IBM has designed and demonstrated a 2D mesh-based Analog Compute-In-Memory accelerator for DNN inference, pictured in Figure 1. The accelerator consists of a mesh of nodes, containing a mix of analog-compute tiles that perform efficient Vector-Matrix Multiplications (VMMs), and digital tiles to handle intermediate digital operations. This accelerator is capable of performing inference at significantly lower latencies and with better power efficiency in comparison to SotA works. One challenge of such mesh-based architectures is that of routing, namely, how are network layers and operations mapped onto the mesh in order to reduce latencies and avoid mesh contention. Such challenges are analogous to those found in fields such as digital circuit and FPGA synthesis, where such algorithms have been studies for decades and a wide variety of open-source libraries are already available.

In this project, the student will: 1. Study prior art on routing techniques 2. Familiarize themselves with the existing mesh-based architecture 3. Propose and test applicable routing strategies and/or develop new routing strategies.

Status: Available

- Looking for master or semester thesis students

- Supervisor: Dr. William Simon: <william.simon1@ibm.com>

Prerequisites

- Outstanding programming skills (C/C++ and/or Python)

- Independent learning/working abilities

- Interest in FPGAs and/or digital synthesis flows (note that work will not be with FPGAs or digital synthesis, but applying applicable routing algorithms to mesh-based architectures)

- Strong work ethic

Character

- 20% Literature review

- 20% Theory

- 60% Design

Professor

Prof. Taekwang Jang <tjang@ethz.ch>

Working Location

The work will take place at the IBM Rüschlikon campus