Difference between revisions of "Vector Processor for In-Memory Computing"

From iis-projects

| Line 1: | Line 1: | ||

| − | [[File:Hmc.jpg|400px|right | + | [[File:Hmc.jpg|400px|right Image from http://www.extremetech.com/computing/167368-hybrid-memory-cube-160gbsec-ram-starts-shipping-is-this-the-technology-that-finally-kills-ddr-ram]] |

==Short Description== | ==Short Description== | ||

Revision as of 13:26, 3 March 2015

Contents

Short Description

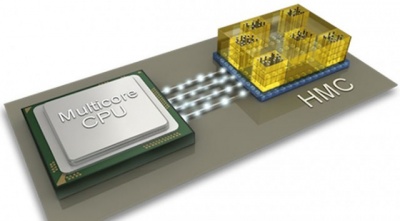

Currently, 3D integration technologies are becoming mature enough for commercialization. Among the first appearing products are so called hybrid memory cubes (HMC's), which consist of several stacked DRAM dies and a logic base layer. Such HMC's can deliver very high bandwidth with much lower energy footprint than today's external DRAM devices.

The logic base layer currently only contains the memory controllers and fast serial transmitters, but due to the large DRAM die sizes there is still a significant amount of unused silicon area. Therefore, this logic layer could host many other components such as processors and other hardware accelerators - and these would have direct access to the DRAM. The concept of such "in-memory computing" architectures has already been around for decades, but so far it has not been viable on an industrial scale. Recent developments in process technology combined with industrial efforts to bring them to the market have now changed this picture.

The aim of this project is to develop a simple vector processor which can be used as a processor in memory (PIM) element. During the thesis you are going to study ongoing related work and perform a thorough architectural exploration. Also, you should look into how the host and PIM(s) could interact via the shared DRAM or using a direct communication protocol. Architectural simulations will be performed using the Gem5 simulation framework. If there is enough time, the developed architecture shall also be implemented on the RTL level.

Status: Available

- Scope: Master Thesis

- Looking for 1-2 Interested Students

- Supervisors: Frank Gürkaynak, Michael Schaffner

Prerequisites

- VLSI I & II

- Interest in processor design

- Matlab, VHDL (or Verilog) and C++

Character

- 25% Theory & Literature Study

- 40% Architecture Design & Exploration

- 35% HDL Implementation