Difference between revisions of "Wireless Communication Systems for the IoT"

From iis-projects

(→Other Available Projects) |

|||

| Line 40: | Line 40: | ||

* [[User:Lstefan|Stefan Lippuner]] | * [[User:Lstefan|Stefan Lippuner]] | ||

| + | |||

| + | * [[User:Weberbe|Benjamin Weber]] | ||

==Professor== | ==Professor== | ||

Revision as of 13:47, 18 September 2017

Contents

Introduction

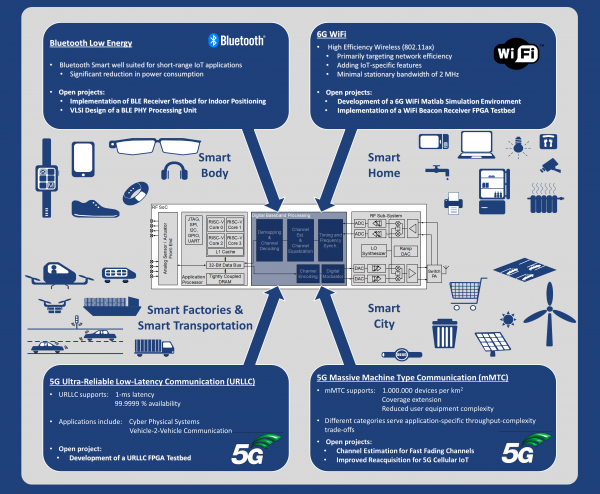

The Internet of Things (IoT) is believed to be one of the main drivers for the semi-conductor industry in the upcoming years. While the key IoT applications will manifest themselves in the near future, it is already clear today, that the use cases will have application-specific requirements. With some applications require high data throughput (e.g. use cases incorporating high-quality video streaming), other use cases rely on extremely low-energy (wearables, implantable telemetry devices), low-latency (self-driving cars), extended link distance (remote sensor networks, drones), and/or location services (self-driving cars, drones).

With some of the requirements contradicting each other (like high-throughput and extremely low energy) it immediately become clear that: No communication system can fit all! Additionally, the very strong cost and form-factor pressure demands for single chip solutions, which incorporate analog sensor / actuator front ends, RF-transceiver, digital baseband processing, and an application processor. Such a RF System-on-Chip (RF-SoC) is mandatory to achieve minimal manufacturing costs.

The unique combination of research fields at the integrated systems laboratory enables the design of complete highly optimized IoT-targeting RF SoC. One part of such an RF SoC design is the hardware- and energy-efficient realization of the digital baseband algorithms in which we constantly offer various semester and master projects in the following fields:

• Development of dedicated communication protocols for IoT

• Development of hardware-efficient digital-baseband algorithms

• Implementation and evaluation of physical communication links on FPGA-testbeds

• ASIC Implementation of key building blocks or full RF-SoC in state-of-the-art CMOS technologies

Available ASIC Design Projects

Other Available Projects

- High-Speed Digital-to-Analog Converter (DAC) for massive MIMO testing in 65nm CMOS

- High-Speed SAR ADC for next generation wireless communication in 12nm FinFET

- Analog building blocks for mmWave manipulation

- A mmWave Voltage-Controlled-Oscillator (VCO) for beyond 5G applications

Analog design projects are also available.