VLSI Implementation of a Low-Complexity Channel Shortener for 2G EC-GSM-IoT and Evolved EDGE

From iis-projects

Contents

Short Description

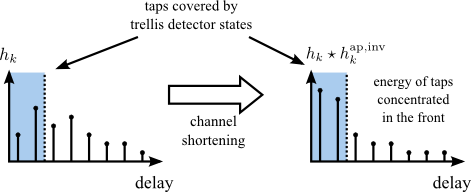

Today's wireless devices have to deal with multi-path propagation caused by reflecting objects along the receive paths. These reflections lead to a long channel impulse responses, which makes the channel equalization complex. Therefore channel shortening filters are used to transform the long channel impulse response into a shorter one. At IIS during the last years, several channel shortening algorithms and implementations have been presented.

Your task in this project is to design and implement a hardware architecture of a novel channel shortening algorithm we developed recently. You will get a MATLAB implementation of the algorithm as a reference implementation, from which you can start building your architecture. After you sketched a block diagram, you will implement the architecture in VHDL. To this end you will port the implementation to an FPGA and analyze resource utilization, or synthesize it for an ASIC implementation, depending if you want to do a semester or a Master project.

Status: Available

- Looking for interested students

- Supervision: Harald Kröll, Benjamin Weber

Character

- 30% Theory/Matlab

- 70% VHDL

Prerequisites

- VLSI I

- Matlab, VHDL

Professor

References

[1] http://www.iis.ee.ethz.ch/~kroell/papers/Ungerboeck_CS.pdf