Difference between revisions of "Digital"

From iis-projects

m (→Deep Learning) |

|||

| Line 1: | Line 1: | ||

| − | + | __NOTOC__ | |

| − | + | [[File:Project_map_2017_10.png|1024px]] | |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | [[ | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

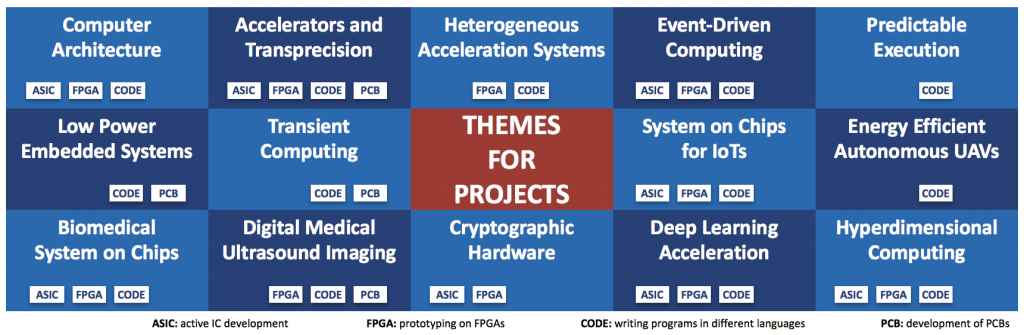

| + | ==Topics for Projects== | ||

| + | * [[Computer Architecture]] | ||

| + | * [[Acceleration and Transprecision]] | ||

| + | * [[Heterogeneous Acceleration Systems]] | ||

| + | * [[Event-Driven Computing]] | ||

| + | * [[Predictable Execution]] | ||

| + | * [[Low Power Embedded Systems]] | ||

| + | * [[Transient Computing]] | ||

| + | * [[System on Chips for IoTs]] | ||

| + | * [[Energy Efficient Autonomous UAVs]] | ||

| + | * [[Biomedical System on Chips]] | ||

| + | * [[Digital Medical Ultrasound Imaging]] | ||

| + | * [[Cryptography|Cryptographic Hardware]] | ||

| + | * [[Deep Learning Projects|Deep Learning Acceleration]] | ||

| + | * [[Hyperdimensional Computing]] | ||

==Active Projects== | ==Active Projects== | ||

These are the projects that are currently active | These are the projects that are currently active | ||

| Line 147: | Line 71: | ||

category = 2011 | category = 2011 | ||

</DynamicPageList> | </DynamicPageList> | ||

| + | [[Category:Computer Architecture]] | ||

| + | [[Category:Acceleration and Transprecision]] | ||

| + | [[Category:Heterogeneous Acceleration Systems]] | ||

| + | [[Category:Event-Driven Computing]] | ||

| + | [[Category:Predictable Execution]] | ||

| + | [[Category:Low Power Embedded Systems]] | ||

| + | [[Category:Transient Computing]] | ||

| + | [[Category:System on Chips for IoTs]] | ||

| + | [[Category:Energy Efficient Autonomous UAVs]] | ||

| + | [[Category:Biomedical System on Chips]] | ||

| + | [[Category:Digital Medical Ultrasound Imaging]] | ||

| + | [[Category:Cryptography]] | ||

| + | [[Category:Deep Learning Acceleration]] | ||

| + | [[Category:Hyperdimensional Computing]] | ||

Revision as of 08:39, 7 November 2017

Topics for Projects

- Computer Architecture

- Acceleration and Transprecision

- Heterogeneous Acceleration Systems

- Event-Driven Computing

- Predictable Execution

- Low Power Embedded Systems

- Transient Computing

- System on Chips for IoTs

- Energy Efficient Autonomous UAVs

- Biomedical System on Chips

- Digital Medical Ultrasound Imaging

- Cryptographic Hardware

- Deep Learning Acceleration

- Hyperdimensional Computing

Active Projects

These are the projects that are currently active

- ASR-Waveformer

- GDBTrace: A Post-Simulation Trace-Based RISC-V GDB Debugging Server (1S)

- A RISC-V ISA Extension for Scalar Chaining in Snitch (M)

- Designing a Scalable Miniature I/O DMA (1-2B/1-3S/M)

- Fault-Tolerant Floating-Point Units (M)

- Creating a Free and Open-Source Verification Environment for Our New DMA Engine (1-3S/B)

- Implementation of a Cache Reliability Mechanism (1S/M)

- Efficient collective communications in FlooNoC (1M)

- On-Board Software for PULP on a Satellite

- A RISC-V fault-tolerant many-core accelerator for 5G Non-Terrestrial Networks (1-2S/B)

- Zephyr RTOS on PULP

- Investigation of Quantization Strategies for Retentive Networks (1S)

- Streaming Layer Normalization in ITA (M/1-2S)

- Physical Implementation of ITA (2S)

- 3D Matrix Multiplication Unit for ITA (1S)

- Virtual Memory Ara

- New RVV 1.0 Vector Instructions for Ara

- Big Data Analytics Benchmarks for Ara

- Creating A Technology-independent USB1.0 Host Implementation Targetting ASICSs (1-3S/B)

- Runtime partitioning of L1 memory in Mempool (M)

- Vector-based Manycore HPC Cluster Exploration for 5G Communication Algorithm (1-2M)

- Radiation Testing of a PULP ASIC

- On - Device Continual Learning for Seizure Detection on GAP9

- Ternary Neural Networks for Face Recognition

- Coherence-Capable Write-Back L1 Data Cache for Ariane (M)

- Efficient TNN compression

- Event-Driven Vision on an embedded platform

- ASIC Development of 5G-NR LDPC Decoder

- Channel Estimation for 5G Cellular IoT and Fast Fading Channels

- An all Standard-Cell Based Energy Efficient HW Accelerator for DSP and Deep Learning Applications

Completed Projects

These are projects that were completed in the last few years

2017

- A computational memory unit using phase-change memory devices

- Deep Learning for Brain-Computer Interface

- Low-Energy Cluster-Coupled Vector Coprocessor for Special-Purpose PULP Acceleration

- Turbo Equalization for Cellular IoT

- Sensor Fusion for Rockfall Sensor Node

- Development of a Rockfall Sensor Node

- FPGA Optimizations of Dense Binary Hyperdimensional Computing

- Fast and Accurate Multiclass Inference for Brain–Computer Interfaces

- A Wireless Sensor Network for a Smart Building Monitor and Control

- BigPULP: Multicluster Synchronization Extensions

- Sub Noise Floor Channel Estimation for the Cellular Internet of Things

- PULPonFPGA: Lightweight Virtual Memory Support - Page Table Walker

- StoneEDGE: An EC-GSM-IoT and Evolved EDGE PHY ASIC

2016

- A Recurrent Neural Network Speech Recognition Chip

- Efficient NB-IoT Uplink Design

- Internet of Things Network Synchronizer

- Accelerator for Boosted Binary Features

- Accelerator for Spatio-Temporal Video Filtering

- Interfacing PULP with a Brain-Inspired Ultra-Low Power Spiking Cochlea

- Design and Implementation of Digital Spiking Neurons for Ultra-Low-Power In-Cluster Coprocessors

- System Analysis and VLSI Design of NB-IoT Baseband Processing

- High-speed Scene Labeling on FPGA

- Learning Image Decompression with Convolutional Networks

- FPGA System Design for Computer Vision with Convolutional Neural Networks

- PULPonFPGA: Lightweight Virtual Memory Support - Multi-Level TLB

- Implementing Hibernation on the ARM Cortex M0

- High-Throughput Hardware Implementations of Authenticated Encryption Algorithms

- Spatio-Temporal Video Filtering

- PULPonFPGA: Lightweight Virtual Memory Support - Coherency Extensions

2015

- Hardware Accelerated Derivative Pricing

- Glitches Reduce Listening Time of Your iPod

- FFT-based Convolutional Network Accelerator

- Real-Time Optical Flow Using Neural Networks

- EvaLTE: A 2G/3G/4G Cellular Transceiver FMC

- Synchronisation and Cyclic Prefix Handling For LTE Testbed

- An FPGA-Based Testbed for 3G Mobile Communications Receivers

- Reading The GSM Beacon Carrier with OsmocomBB and stoneEDGE

- Baseband Meets CPU

- Active-Set QP Solver on FPGA

- Vector Processor for In-Memory Computing

- StoneEDGE: An EC-GSM-IoT and Evolved EDGE PHY ASIC

- Hardware/software co-programming on the Parallella platform

- Design and VLSI Implementation of a Constrained-Viterbi Algorithm Equalizer for 3GPP TD-HSPA

- Time and Frequency Synchronization in LTE Cat-0 Devices

- Real-Time Stereo to Multiview Conversion

2014

- EvalEDGE: A 2G Cellular Transceiver FMC

- Real-Time Stereo to Multiview Conversion

- Design and Implementation of a Convolutional Neural Network Accelerator ASIC

- Design and Implementation of an Approximate Floating Point Unit

2013

- RazorEDGE: An Evolved EDGE DBB ASIC

- Real-Time Stereo to Multiview Conversion

- NORX - an AEAD algorithm for the CAESAR competition

- A Unified-Multiplier Based Hardware Architecture for Elliptic Curve Cryptography

- SHAre - An application Specific Instruction Set Processor for SHA-2/3

- Quantum Key Secured 100 Gbit/s Payload Encryption and its High-Speed Network Interfaces

- Feature Extraction with Binarized Descriptors: ASIC Implementation and FPGA Environment

- Real-time View Synthesis using Image Domain Warping

- Ultra-low power processor design

2012

- A Multiview Synthesis Core in 65 nm CMOS

- Real-time View Synthesis using Image Domain Warping

- High-Throughput Authenticated Encryption Architectures based on Block Ciphers

2011

Categories:

- Computer Architecture

- Acceleration and Transprecision

- Heterogeneous Acceleration Systems

- Event-Driven Computing

- Predictable Execution

- Low Power Embedded Systems

- Transient Computing

- System on Chips for IoTs

- Energy Efficient Autonomous UAVs

- Biomedical System on Chips

- Digital Medical Ultrasound Imaging

- Cryptography

- Deep Learning Acceleration

- Hyperdimensional Computing