Search results

From iis-projects

Create the page "System" on this wiki! See also the search results found.

Page title matches

- ...t role in this type of devices and in general in battery-operated embedded system. : Interest in Computer Architectures at system level2 KB (342 words) - 16:46, 11 February 2015

- ...o experienced students) comprises the implementation of such a measurement system. Possible approaches include a cross-correlating spectrum analyzer or the u2 KB (251 words) - 20:06, 17 February 2015

-

40 bytes (3 words) - 14:01, 26 March 2015

- ...s, microprocessors, FPGAs and get a demonstrator to work. Depending on the system this may require you to: * Program a microcontroller or a microprocessor system122 members (0 subcategories, 0 files) - 17:03, 3 February 2015

- : Interest in Computer Architectures at system level ...arning would be beneficial (i.e. semester project or exam done in Wearable system I prof. Troester)3 KB (380 words) - 11:59, 28 July 2015

- ...hose in our prototype, and otherwise improve it by building a more compact system, adding communication capabilities to transmit suspicious cases to a remote [[Category:Digital]] [[Category:System]] [[Category:Semester Thesis]] [[Category:Group Work]]8 KB (1,176 words) - 16:26, 30 October 2020

-

2 KB (245 words) - 10:39, 6 November 2017

- [[File:origami-fpga-system.png|400px|thumb]] ...o finish the processing pipeline (activation, pooling), and completing the system by connecting a camera or loading a video stream and displaying the results3 KB (397 words) - 18:17, 29 August 2016

File:Origami-system-v03.pdf (272 KB) - 12:20, 14 December 2015- [[Category:System Design]]4 KB (555 words) - 16:36, 23 May 2018

- ...al-world handset operations in the wide-band code-division multiple-access system. Large-frequency and clock errors are induced at initial search due to an i2 KB (340 words) - 10:39, 6 November 2017

- ..., televisions, pc among others. The main goal is to achieve an intelligent system that process the data from one or more sensors to understand the context an ...classification accuracy and energy efficiency and to further optimize the system.5 KB (669 words) - 17:22, 31 January 2018

- Using mixed-signal SoCs developed at IIS it is possible to integrate a system to conducting medical research. Despite low power consumption of the system the3 KB (366 words) - 13:05, 27 April 2018

- #REDIRECT [[System Analysis and VLSI Design of LTE NB-IoT Baseband Processing]]79 bytes (11 words) - 09:49, 19 October 2016

- #REDIRECT [[System Analysis and VLSI Design of NB-IoT Baseband Processing]]75 bytes (10 words) - 09:49, 19 October 2016

- #REDIRECT [[WCDMA/HSPA+ Synchronization System Design, Implementation, and Testing]]84 bytes (9 words) - 15:33, 1 December 2016

- ...his project we would like to develop a concrete proof of concept low power System-on-Chip where (small) practical applications such as Spiking Convolutional ...connected. With regard to this, a higher-level synaptic array for the full System-on-Chip must be designed, taking into account even more strict area constra7 KB (1,000 words) - 12:22, 13 January 2017

- ...classification accuracy and energy efficiency and to further optimize the system. [[Category:System Design]]5 KB (703 words) - 17:21, 31 January 2018

- ...bedded image processing. The ambitious goal is to build a self-sustainable system that allows simple image processing to be implemented on-board the device. ...dy the required components for building a miniature ultra-low power camera system and develop a demonstration platform based on our ULP image sensor chip (de4 KB (602 words) - 10:45, 31 January 2023

- #REDIRECT [[System on Chips for IoTs]]1 member (0 subcategories, 0 files) - 08:34, 7 November 2017

- #REDIRECT [[Biomedical System on Chips]]3 members (0 subcategories, 0 files) - 08:35, 7 November 2017

-

48 bytes (8 words) - 11:25, 7 November 2017

-

0 bytes (0 words) - 19:23, 23 November 2022

- ...he student he can be involved on the design of the IC, the layout, or at a system and application levler. The wake-up receiver should achieves power consumpt ...classification accuracy and energy efficiency and to further optimize the system.5 KB (686 words) - 11:54, 2 February 2018

-

4 KB (605 words) - 16:35, 20 February 2018

- ...hanism both for sub-systems on the chip level as well as components on the system level, e.g. flash memory or radio ICs. This project focuses on chip-level d ...dictates battery size, the most critical factor in any volume-constrained system.4 KB (597 words) - 16:57, 12 July 2022

-

0 bytes (0 words) - 14:44, 23 May 2018

- ..., non-invasive method to measure kidney performance via an external sensor system to avoid the use of urinary catheters for this subgroup of patients, thereb ...classification accuracy, and energy efficiency and to further optimize the system. The work includes the modeling and design of a suited impedance sensor, it6 KB (857 words) - 15:37, 10 November 2020

- ...roject focusses on the development of an unobtrusive multisensory embedded system to assist coaches to better quantify jumping trajectories of athletes. With ...perceptible to the athlete so as not to disturb his/her sensitive jumping system.6 KB (820 words) - 12:13, 23 July 2023

- ...pikes due to cosmic rays being captured by sequential elements, taking the system into a faulty state.6 KB (980 words) - 14:46, 2 June 2021

- #REDIRECT [[PULP in space - Fault Tolerant PULP System for Critical Space Applications]]88 bytes (13 words) - 13:10, 9 August 2019

- ...rphic intelligence using their processor to build a whole working embedded system. The student will deal with both hardware and software building a prototype * Motivation to build and test a real system5 KB (692 words) - 15:45, 10 November 2020

- ...ock diagram, which involves both the programming of a Low power FPGA and a System on Chip with ARM cortex-M4F and Bluetooth low energy 5.0. The project is qu * Motivation to build and test a real system4 KB (526 words) - 15:48, 10 November 2020

- <!-- Manycore System on FPGA --> At ETH, we are developing our own many-core system called MemPool [1]. It boasts 256 lightweight 32-bit Snitch cores developed8 KB (1,319 words) - 10:41, 6 July 2021

-

0 bytes (0 words) - 12:48, 2 November 2020

-

0 bytes (0 words) - 12:16, 2 November 2020

- ...s is to have Halide programmed image processing kernels running on an HERO system implemented on an FPGA.5 KB (737 words) - 17:26, 2 November 2020

- <!-- (M): A Flexible Peripheral System for High-Performance Systems on Chip --> One of the most tedious and error-prone steps is assembling a peripheral system with the required and desired IO; this usually involves adapting existing p11 KB (1,675 words) - 15:40, 15 March 2021

- #REDIRECT [[Implementation of a Heterogeneous System for Image Processing on an FPGA (S)]]90 bytes (13 words) - 17:26, 2 November 2020

- ...s private memory banks---this, however, impacts the programmability of the system. ...eved through a cache hierarchy, which impacts the energy efficiency of the system through its non-negligible power consumption.8 KB (1,196 words) - 10:41, 6 July 2021

- #REDIRECT [[Physical Implementation of MemPool, PULP's Manycore System (1M/1-2S)]]82 bytes (11 words) - 17:40, 2 November 2020

- ...ludes them from being used in a portable system. Furthermore, surveillance system typically do not come with any localized intelligence, so their recorded da In this project, a novel, distributed and energy-efficient surveillance system will be brought up and optimized by the student.3 KB (433 words) - 15:36, 4 August 2022

- <!-- Peripheral Event Linking System For Real-Time Capable Energy-Efficient SoCs (M/1-2S) --> ...unities are limited due to the necessity to retain major parts of the main system memory due to the use of static random access memory (SRAM) for code execut8 KB (1,127 words) - 19:54, 1 March 2023

- ...ormation on the structure of musculoskeletal tissues, organs, and vascular system. The velocity of liquid flows (as for arteries and veins) can be measured b Preliminary results of custom syringe pump system:3 KB (363 words) - 17:18, 3 May 2024

- At ETH, we developed our own many-core system called MemPool. It boasts 256 lightweight 32-bit Snitch cores. They impleme ...d to integrate an FLL, a boot ROM, and a JTAG to access and initialize the system. While there are many IPs and know-how at IIS for that, this is also highly8 KB (1,239 words) - 12:36, 29 January 2024

- ...ed Hardware Accelerator to achieve the next 10x in Energy Efficiency: Full System Integration (2S,1M) --> ...ople.ee.ethz.ch/~janniss/projects/Maddness_system_integration.pdf Maddness System Intergration]6 KB (846 words) - 16:50, 3 November 2022

- <!-- AXI-based Network on Chip (NoC) system --> ...ould be to build a system with a mesh NoC and a couple of cores and do the system integration for a potential tapeout. For the verification, low-level softwa2 KB (252 words) - 14:43, 23 October 2023

-

2 KB (250 words) - 09:31, 29 August 2023

- ...n technique is to combine multiple instances of a core to a ''multi-core'' system. This technique introduces a new challenge: Each core keeps its own copy of ...ane cores. Throughout this project, the feasibility and performance of the system shall be evaluated.2 KB (260 words) - 16:41, 15 November 2022

- ...Qubits will be read-out at the same time. For discrete Qubits, the readout system usually works at the sub-1 GHz frequency range. However, for a compact foot2 KB (372 words) - 10:32, 14 February 2023

- ...t needs to be accessed and monitored calls for a high-speed FPGA/GPU based system with a compact, and incubator-compatible hardware design. [[Image:Hangxing FPGA.png|800px| System Overview]]6 KB (720 words) - 16:27, 27 September 2023

- ...n a limited power budget require a novel approach across the entire stack, system-level design, and optimization. ...red offchip]] [[File:DistributedOnSensor.png|500px|thumb|right|Distributed System -> Only Region of Interest section of image is transferred offchip]]4 KB (577 words) - 18:28, 4 October 2023

- In this project, you will develop a smart agriculture system utilizing a sensor platform to optimize irrigation and pest control, aiming4 KB (534 words) - 17:09, 16 May 2024

- ...egrity. The end goal is to deploy these models into a real-time monitoring system capable of issuing alerts to maintenance teams, thus facilitating prompt an3 KB (465 words) - 11:47, 14 May 2024

- #REDIRECT [[Structural Health Monitoring (SHM) System (1-2S/M)]]64 bytes (9 words) - 11:47, 14 May 2024

- ...on of your project will be the development of a sophisticated notification system designed to automatically alert both local authorities and the public about * '''Automated Warning System:''' Develop a notification system that automatically alerts local authorities and the public of potential dan4 KB (531 words) - 17:09, 16 May 2024

Page text matches

- * [[Noise Figure Measurement for Cryogenic System]] * [[A FPGA-based data streaming system that enables real-time monitoring of cell culture and neuroactivities]]5 KB (540 words) - 12:31, 8 May 2024

- ...er, there is a lot of functionality which will never be used in the target system and it is therefore not necessary to maintain all this functionality. Remov ...Adding User I/O to the Processor''': If the processor is not embedded in a system, it is like a blackbox which computes something and stores the result in th10 KB (1,669 words) - 19:01, 30 January 2014

- ...ilog code, is the '''emacs''' editor, as it has a really advanced VHDL and System Verilog mode. Because of this, you should get comfortable with the idea of841 bytes (137 words) - 14:42, 16 January 2014

- dynamically modify the timing constrains aiming to tolerate at system level reliable computing system in nano-meter technology operating in3 KB (409 words) - 10:52, 27 March 2014

- [[Category:System on Chips for IoTs]] [[Category:Biomedical System on Chips]]4 KB (397 words) - 15:44, 14 February 2023

- ...-process this data in order to compact it for the transport to the imaging system. A special challenge pose the high-speed output pin drivers. In case of int ...o reduce the incidental data rates between the sensor head and the backend system, and second, new beamforming strategies to minimize the computational burde4 KB (614 words) - 20:10, 17 February 2015

- ...tion of this work is to provide the means for achieving a portable medical system that can provide high-quality images while being battery operated, and thus ...latform utilization and efficiency. One of the distinctive features of the system will be to support a qualified software deployment and maintenance model wh18 members (0 subcategories, 0 files) - 15:06, 17 January 2014

- TD-SCDMA is a 3GPP standard that combines an advanced TDMA/TDD system with an adaptive CDMA component operating in a synchronous mode. Its TDD na1 KB (206 words) - 14:07, 9 February 2015

- TD-SCDMA is a 3GPP standard that combines an advanced TDMA/TDD system with an adaptive CDMA component operating in a synchronous mode. Its TDD na1 KB (160 words) - 11:17, 23 September 2016

- ...le or strechable materials to form wearable and conformable devices. These system are often composed of various flexible, bendable but also small ridgid comp4 KB (444 words) - 12:43, 23 July 2023

- ...ure in such a way that later studies will allow '''ML-based control of the system'''. ...architecture is to be designed in such a way that ML-based control of the system is possible.6 KB (741 words) - 18:14, 21 July 2023

- TD-SCDMA is a 3GPP standard that combines an advanced TDMA/TDD system with an adaptive CDMA component operating in a synchronous mode. Its TDD na1 KB (158 words) - 11:17, 23 September 2016

- TD-HSPA is a 3GPP standard that combines an advanced TDMA/TDD system with an adap- MLSD computation for a system with such dimensions practically impossible given the current5 KB (684 words) - 10:43, 6 November 2017

- ...ject, you will assess the effect of carrier aggregation in an LTE-Advanced system. You will start by implementing a MATLAB framework to simulate the LTE-Adva3 KB (405 words) - 16:13, 29 December 2016

- ...he chance to develop and test a transmitter for a 3G mobile communications system. The IIS is currently working on a receiver for TD-HSPA, a 3G standard emer ...ring the VLSI III lecture. For an implementation on an FPGA, the resulting system (combined with the existing analog transceiver) can be tested using a proto3 KB (382 words) - 20:00, 26 September 2017

- * Digital circuit and system design (FPGA/ASIC)922 bytes (125 words) - 12:42, 1 June 2017

- Forward error correction is a crucial part in any communication system, since it enables reliable transmission over unreliable channels. In mobile3 KB (508 words) - 11:12, 14 April 2016

- Ultra Low Power System on a Chip (UlpSoC) is the flagship project at the IIS that aims to design e8 members (0 subcategories, 0 files) - 19:42, 16 January 2014

- ...ill form the standard chip to chip communication standard for the [[PULP]] system.3 KB (492 words) - 12:34, 7 November 2017

- applications for this system is in real-time video applications, expecially system, improving the energy efficiency of the system. The accelerator will3 KB (407 words) - 10:57, 5 November 2019

- The IIS 2G testbed has no operating system (OS) running on [4] FreeRTOS - Market leading RTOS (Real Time Operating System) for embedded systems3 KB (421 words) - 10:40, 6 November 2017

- ...tp://www.freertos.org/ FreeRTOS - Market leading RTOS (Real Time Operating System) for embedded systems with Internet of Things extensions], June 2015.2 KB (273 words) - 11:30, 24 February 2017

- ...data over a wireless link. Some of these system even include an actuation system, which reacts depending on the captured data. ...nnected and operate and act collaboratively it is called a 'cyper-physical system' (CPS).3 KB (418 words) - 11:24, 10 November 2017

- ...tion of the FPUs and therefore reduce the overall power consumption of the system. Sharing FPUs allows to employ several different units, which can be either ...nd is a promising approach to further improve the energy efficiency of the system. One way to approximate FP-operations is to use Newton's method to compute3 KB (377 words) - 10:58, 21 February 2018

- ...egory:Qcrypt|QCRYPT]] was the development of the 100 Gbit/s link encryptor system with a variety of optical interfaces on the plain-text side and a 100 Gbit ...main focus lay on the development of a second version of the PCB for this system. The layer stackup was modified to enhance the high-frequency quality of th2 KB (359 words) - 20:06, 17 February 2015

- ''2012 IEEE/IFIP 20th International Conference on VLSI and System-on-Chip (VLSI-SoC)'', Santa Cruz, California, USA, 7-10 Oct 20123 KB (392 words) - 12:25, 26 March 2015

- ...of quantum mechanics. However, existing systems are too slow. The new QKD system will be capable of producing keys at 1 Mbps rate, which means it will allow2 members (0 subcategories, 0 files) - 17:27, 28 January 2014

- ...erent mobile platforms, most productions are captured with one acquisition system at fixed parameters. Examples for content adaption algorithms are content-a ...ons and VLSI Implementations", ''VLSI-SoC: From Algorithms to Circuits and System-on-Chip Design, volume 418 of IFIP Advances in Information and Communicatio4 KB (520 words) - 16:04, 13 May 2015

- ...IC/FPGA system which implements the first three steps of this process. Our system is able to extract SKB features from one 720p video stream in real time (303 KB (487 words) - 15:57, 13 May 2015

- ...ing and embedded heterogeneous systems on a chip with a focus on operating system, driver, runtime and programming model support for efficient and transparen1 KB (193 words) - 15:39, 3 March 2020

- ...the image is being acquired and forward this information to a larger host system for further processing. ...algorithm steps directly ion hardware and interface with the host computer system.3 KB (357 words) - 18:53, 6 December 2014

- ...bits. Such data converters are intended to be embedded in a mostly digital system, and this legitimates the adoption of ultra-scaled CMOS technologies from w2 KB (277 words) - 17:28, 29 January 2014

- ...ying downscaling of CMOS technology to the nano scale device size and tera system complexity. This aggressive downscaling has allowed the number of transisto ...stem functionality into digital, analog and RF or sensor realizations on a system on chip optimally is one of the key topics that will impact the era of nano7 members (0 subcategories, 2 files) - 17:31, 29 January 2014

- ==Implantable/Wearable System for on-line Monitoring of Human Metabolic Conditions== ...surements, while at the same time reducing analysis time and cost. The new system will investigate many different metabolic compounds of interest in cardiova1 member (0 subcategories, 0 files) - 18:14, 29 January 2014

- Although the wireless and battery-powered nature of this system reduces the impact of mains interference, its amplitude might nonetheless b ...ed by an off-the-shelf mobile phone battery which is sufficient to run the system for several hours - the battery life-time is mainly limited by the Bluetoot2 KB (280 words) - 10:54, 10 March 2015

- his PhD thesis entitled "An Evolved EDGE System on Chip for the Cellular894 bytes (115 words) - 17:17, 30 November 2021

- [[Category:System on Chips for IoTs]] [[Category:Biomedical System on Chips]]5 KB (597 words) - 12:56, 4 December 2021

- ...upper layers of the OsmocomBB GSM protocol stack. The functionality of the system is verified with a testbed comprising a base station and a receiver board w3 KB (360 words) - 14:14, 27 May 2015

- ...ssor and the unit where RLC blocks are processed for IR is attached to the system processor. The decoding of the RLC blocks takes place on a PHY Digital Sign3 KB (397 words) - 14:12, 27 May 2015

- ...ons such as those in the time-duplexing high speed packet access (TD-HSPA) system.2 KB (266 words) - 10:43, 9 February 2015

- ...terms of parallelism, performances and robustness. One has to revisit the system design in terms of usage of hardware accelerators, heterogeneous or homogen4 KB (568 words) - 12:48, 9 February 2015

File:Exploitation of Inherent Error Resilience of Wireless Systems.png ...communication system (receive side). Bottom: Throughput performance of the system including re-transmissions with hybrid-ARQ for various defect rates.(631 × 581 (187 KB)) - 10:33, 4 February 2014- ...communication system (receive side). Bottom: Throughput performance of the system including re-transmissions with hybrid-ARQ for various defect rates.]] ...Q operation that is critical for the average throughput performance of the system.2 KB (343 words) - 13:56, 9 February 2015

File:Data Mapping for Unreliable Memories.png ...channel with unreliable memory. Bottom: Bit-error rate performance of the system assuming convolutional coding for different data representations.(631 × 539 (130 KB)) - 10:39, 4 February 2014- ...channel with unreliable memory. Bottom: Bit-error rate performance of the system assuming convolutional coding for different data representations.]] ...ion-specific cost functions) substantially increases the robustness of the system to unreliable memory operation, compared to the data representations most c3 KB (352 words) - 13:56, 9 February 2015

- ...t role in this type of devices and in general in battery-operated embedded system. : Interest in Computer Architectures at system level2 KB (342 words) - 16:46, 11 February 2015

- ...sor and actuator networks (WSANs) possible. These networks are distributed system consisting of nodes with sensors, intelligence and actuator interconnected ...e power consumption reduction, reliability, functionality and optimize the system.3 KB (487 words) - 12:02, 27 January 2016

- ...a low power radio wake up receiver can reduce the power consumption of the system while still keeping its response time low. Another role of the wake-up radi ...and receiver and it could include . Measurements on the performance of the system will be performed from the students in order to evaluate the distance, powe4 KB (613 words) - 19:54, 9 February 2015

- ...ices while still keeping its wake up time low. Another role of the wake-up system is that based on "intelligence" to select a specific device which has to be ...and receiver and it could include . Measurements on the performance of the system will be performed from the students in order to evaluate the distance, powe3 KB (515 words) - 19:55, 9 February 2015

- [[File:FeatureExtractionSystem.jpg|thumb|500px|Current feature extraction system.]] ...rrently used in the video analysis part of a more complex video processing system which performs [[Real-Time_Stereo_to_Multiview_Conversion|automatic multiv3 KB (373 words) - 11:51, 19 August 2017

- ...o experienced students) comprises the implementation of such a measurement system. Possible approaches include a cross-correlating spectrum analyzer or the u2 KB (251 words) - 20:06, 17 February 2015

- ...uld be to evaluate and integrate this camera into a working scene labeling system [[http://dl.acm.org/citation.cfm?id=2744788 paper]] and would be very diver * create a system from the individual parts (build a case/box mounting the cameras, dev board6 KB (941 words) - 11:29, 5 February 2016

- ...e with basic engineering tools (web search, basic usage of Linux operating system, compilers…) and of work independence5 KB (784 words) - 14:50, 30 November 2016

- [[Category:Biomedical System on Chips]]2 KB (278 words) - 16:57, 12 July 2022

- [[Category:System Design]]2 KB (348 words) - 20:01, 26 September 2017

- * Designing the system architecture * Defining the circuit using hardware description languages (HDL) such as (System Verilog or VHDL) for [[:Category:Digital|digital projects]], and schematic1 KB (165 words) - 19:52, 10 February 2015

- * Understand the different available peripherals on your system board * Run your system on the development board and collect the results.1,020 bytes (132 words) - 19:50, 10 February 2015

- ...will be able to control the accelerator from the command line of the Linux system. :[3] [http://www.arm.com/products/system-ip/amba/amba-open-specifications.php ARM AMBA Specification]2 KB (236 words) - 09:46, 12 October 2017

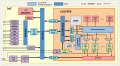

- [[File:pulp_block_diag.png|thumb|400px|Basic block diagram of a PULP system.]] * [http://asic.ethz.ch/2020/Thestral.html Thestral] Snitch based system with 1x cluster (8x compute + 1x DMA core) and 1x governor core. Designed t10 KB (1,563 words) - 10:09, 19 August 2022

- [[Category:System Design]]3 KB (449 words) - 12:12, 4 November 2019

- ...r OpenRISC core with the following capabilities so that a standalone small system can be designed that can directly interface with various sensors and can co : For low power operations, we would like to shutdown most of the system including the processor, and wait until there is an event that requires the4 KB (667 words) - 15:23, 23 December 2016

- In recent years reseach works shows that thermal evolution of a multicore system can be effectively modelled with linear state-space representation enabling ...will then be part of a larger system and be part of the thermal management system. In this project the goal is to implement a novel MPC algorithm in hardware3 KB (456 words) - 08:35, 20 January 2021

- ..., R.N. Challa, and H.A. Mahmoud. Frequency Scan Method for Determining the System Center Frequency for LTE TDD, September 6 2013. WO Patent App. PCT/US2013/02 KB (350 words) - 17:56, 14 April 2016

- ====[[Biomedical System on Chips|Biomedical System on Chips]]==== ...f wireless communication. Our current platform with a multi-core processor system and a great RF transceiver allows us to research upcoming wireless transmis3 KB (369 words) - 18:11, 1 March 2023

- ...method by implementing our system.. Measurements on the performance of the system will be performed from the students in order to evaluate the distance, powe : Interest in Computer Architectures at system level3 KB (378 words) - 19:56, 9 February 2015

- Reliability (R(t)) is the probability that a given system does not fail before time t. It is becoming a major concern in modern multi ...bile]] [[Category:Temperature]] [[Category:Dynamic Management]] [[Category:System Design]]4 KB (573 words) - 17:24, 9 February 2015

- ...s an heterogeneous thermal profile which is highly dependent on the actual system usage. As a matter of fact today and future mobile devices are thermally li ...thermal model can be directly identified from the target device by mean of system identification and self-calibrating routines.3 KB (452 words) - 11:03, 10 February 2015

- [[Category:System Design]]3 KB (408 words) - 13:17, 5 February 2016

- ...stem was proposed alongside the release-8 of the Long Term Evolution (LTE) system for the fourth generation (4G) of mobile communication. While the air inter ...tionality of a standard-compliant physical layer of a mobile communication system. Possibly, the student can also investigate and analyze an interesting perf1 KB (159 words) - 11:16, 23 September 2016

- [1] ''Cellular system support for ultra-low complexity and low throughput Internet of Things (CIo3 KB (384 words) - 16:41, 17 July 2016

- ...E transceiver [2] will be used. You will start with your design by doing a system analysis on the required building blocks (Synchronization, FFT, Symbol dete [[Category:System Design]]3 KB (335 words) - 14:20, 4 November 2019

- : Matlab, C++, VHDL or System Verilog2 KB (351 words) - 13:09, 2 November 2015

- : Matlab, C++, VHDL or System Verilog2 KB (328 words) - 12:38, 1 June 2017

- ...er, a careful design of each regulator is extremely important. A PCB-based system, containing of-the-shelf converter chips where available, and discrete-comp [[Category:System Design]]3 KB (438 words) - 18:06, 3 February 2015

- ...be mapped to both cores. This results in a lower active time, allowing the system to enter a low-power sleep mode, and reduce the total energy consumption.3 KB (431 words) - 18:04, 28 January 2017

- [[Category:System Design]]4 KB (589 words) - 10:14, 3 August 2018

- ...If you are interested in doing something with low-power, energy-efficient system design, just send me an e-mail. There is plenty of room for both theoretica890 bytes (114 words) - 19:10, 28 January 2017

- : Interest in Computer Architectures at system level : Wearable system I (prof. Troester lectures)2 KB (319 words) - 16:24, 30 October 2020

- ...s, microprocessors, FPGAs and get a demonstrator to work. Depending on the system this may require you to: * Program a microcontroller or a microprocessor system122 members (0 subcategories, 0 files) - 17:03, 3 February 2015

- [[File:mvSystem.jpg|thumb|600px|a) Multiview system in action and b) closeup of the hardware prototype.]] Ideally, a 3D display system should not require the users to3 KB (509 words) - 09:09, 23 October 2015

- [[Category:System on Chips for IoTs]] [[Category:Biomedical System on Chips]]7 KB (816 words) - 11:57, 8 May 2024

- ...event-driven simulator designed for simulating IoT processors and complex system-on-chips (SoCs). It plays a crucial role in enabling agile design space exp * Experience with System Verilog is recommended but not strictly necessary4 KB (520 words) - 15:15, 4 December 2023

- ...k, Nitin Mangalvedhe, Amitava Ghosh, and Benny Vejlgaard. Narrowband LTE-M system for M2M communication. 2014.4 KB (561 words) - 10:43, 6 November 2017

File:Pulp block diag.png Block diagram of the PULP system(1,361 × 751 (137 KB)) - 18:47, 7 July 2015- is indispensable. Ideally, System-on-a-Chip (SoC) or System-in-a-Package (SiP) modems such as [1] are7 KB (1,105 words) - 20:02, 26 September 2017

- [[Category:Digital]] [[Category:System Design]]5 KB (707 words) - 11:22, 5 February 2016

- [[Category:System Design]]1 KB (169 words) - 16:42, 9 December 2015

- ...erogeneous uniform memory access (hUMA) as envisioned by the Heterogeneous System Architecture (HSA) foundation, their low-power counterparts targeting the e ...L1 scratchpad memory, and the shared main memory to optimally exploit the system's memory hierarchy and to achieve high performance.5 KB (716 words) - 13:43, 29 November 2019

- ...e piezoelectric elements in the transducer head are connected to a backend system over a large cable containing hundreds of small coaxial cables. This is sho In order to do so, the entire analog frontend of the ultrasound system needs to be integrated into the transducer head and a digital link needs to3 KB (378 words) - 11:52, 10 January 2017

- ...tation of an entire scene labeling network. In order to keep the developed system flexible in terms of the convolutional neural network that is applied as we ...rt software blocks to programmable logic and design an entire hetergeneous system using with software, FPGA fabric and hardwired interfaces.8 KB (1,197 words) - 18:18, 29 August 2016

- [[Category:System Design]]3 KB (420 words) - 11:22, 14 April 2016

- ...erogeneous uniform memory access (hUMA) as envisioned by the Heterogeneous System Architecture (HSA) foundation, their low-power counterparts targeting the e This system design project requires work to be done at several layers of abstraction. M4 KB (585 words) - 17:57, 7 November 2017

- ...erogeneous uniform memory access (hUMA) as envisioned by the Heterogeneous System Architecture (HSA) foundation, their low-power counterparts targeting the e : VHDL/System Verilog, C4 KB (554 words) - 17:57, 7 November 2017

- ...ment of novel zero-power sensors that act as a trigger for the rest of the system when an important event is detected and consume zero-power between two dete ...classification accuracy and energy efficiency and to further optimize the system.6 KB (774 words) - 08:36, 23 November 2022

- [[Category:System Design]] [[Category:System Design]]4 KB (471 words) - 11:13, 3 May 2018

- ...we have implemented and fabricated an 8-channel biosignal acquisition SoC (System-on-Chip) [http://asic.ee.ethz.ch/2014/CerebroV4.0_Homer.html] including ana2 KB (353 words) - 08:35, 20 January 2021

- [[Category:System Design]] [[Category:Completed]] [[Category:Semester Thesis]] [[Category:Luk [[Category:Digital]] [[Category:System Design]]4 KB (563 words) - 11:29, 5 February 2016

- ...classification accuracy and energy efficiency and to further optimize the system. : Interest in Computer Architectures at system level3 KB (448 words) - 11:59, 28 July 2015

- : Interest in Computer Architectures at system level ...arning would be beneficial (i.e. semester project or exam done in Wearable system I prof. Troester)3 KB (380 words) - 11:59, 28 July 2015

- [[Category:System Design]]4 KB (507 words) - 12:11, 16 February 2016